## INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN COMPUTER & COMMUNICATION ENGINEERING

Volume 9, Issue 10, October 2021

**Impact Factor: 7.542**

|| Volume 9, Issue 10, October 2021 ||

| DOI: 10.15680/LJIRCCE.2021.0910031 |

# An Efficient Approach for Reversible Realization of 8- Bit Adder-Subtractor Circuit

KM Binaka Rai<sup>1</sup>, Dr. Anshuj Jain<sup>2</sup>

M.Tech Scholar, Department of Electronics & Communication Engineering, SCOPE College of Engineering, Bhopal, India<sup>1</sup>

Associate Professor & HOD, Department of Electronics & Communication Engineering, SCOPE College of Engineering, Bhopal, India<sup>2</sup>

**ABSTRACT:** Full Adder is the heart of any central processing unit that is a core component employed in all the processors. The approach to minimize power loss from digital devices made researchers to focus on reversible logic. This paper presents design approaches for reversible realization of 8-bit adder-subtractor circuit with optimized quantum cost. This design is compared with existing designs on some selected performance parameters such as total number of reversible gates, garbage outputs and quantum cost. The proposed design for 8-bit adder-subtractor circuit using reversible approach simulated using Modelsim tool and synthesised for Xilinx ISE 14.7.

**KEYWORDS**: Adder, Xilinx, Reversible Realization, Delay, components, Gates.

#### I. INTRODUCTION

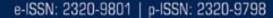

The reversible logic operations can't erase information and dissipate zero heat. The circuit actually operates in a backward operation, allows reproducing the inputs from the outputs and consumes zero power. As the basic elements of any logic circuit, logic gates are used to realize Boolean functions. A Reversible Logic Gate should produce one-to-one map-ping between Inputs and Outputs, so that reversibility is maintained. That is Reversible Gate is Bijective between Inputs and Outputs. It not only helps us to determine the outputs from the inputs but also helps us to uniquely recover the inputs from the outputs. Additional inputs or outputs can be added so as to make the number of inputs and outputs equal whenever necessary. This also refers to the number of outputs which are not used in the synthesis of a given function. In certain cases these become mandatory to achieve reversibility. Inputs + Constant Inputs = Outputs + garbage figure 1 shows a n-input and n-output Reversible Logic Gate and is called as n\*n Reversible logic gate, where nth input of logic gate is given by In and nth output is given by On.

Figure 1: n\*n Reversible Logic Gate

| Volume 9, Issue 10, October 2021 |

| DOI: 10.15680/LJIRCCE.2021.0910031 |

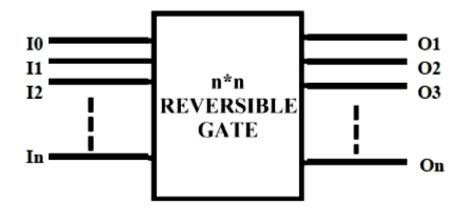

There exist many reversible gates in the literature. Among them 2\*2 Feynman gate (shown in Fig. 2), 3\*3 Feynman Double Gate is the most preferred. The Feynman Gate shown consists of two inputs A and B, two outputs P(= A) and Q(= A B).

Figure 2: Feynman Gate

The simplest Reversible gate is NOT gate and is a 1\*1 gate. Controlled NOT (CNOT) gate is an example for a 2\*2 gate.

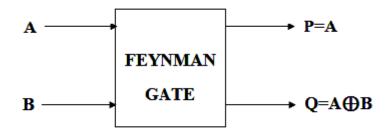

#### II. METHODOLOGY

Figure 3: Flow Chart

The 8-bit adder/subtractor computes the sum or difference of two 8-bit numbers, A and B. This uses our 8-bit carry look ahead adder with 2's complement or and multiplexer to implement subtraction. If the enable bit is set low, then the mux lets through input B and the result is A+B. If the enable bit is set to high, then the mux lets through the output of the complement or, so the adder adds A and the 2's complement of B, which is equivalent to A-B.

|| Volume 9, Issue 10, October 2021 ||

| DOI: 10.15680/LJIRCCE.2021.0910031 |

When performing addition 10100010 + 11100011 (enable set low) the worst case delay on the MUX for the schematic is 0.02975 ns. Add this to the delay needed for the clock of the 8-Bit adder to get a total clock delay of 0.02975ns + 0.110126 ns = 0.139876 ns. So the earliest the schematic clock can switch for addition is 0.14 ns after the inputs are set.

For layout this delay was 0.12012 ns. Add this to the delay from the 8-bit adder to get a total clock delay of 0.12012 ns + 0.259166 ns = 0.379286 ns. So the earliest the extracted clock can switch for addition is 0.38 ns after the inputs are set.

When performing subtraction 10100010 - 00000001 (enable set high) the worst case delay for the complementor for the schematic is 0.74565 ns. The worst case delay for the mux for the schematic is 0.05439 ns. So together they create a total delay of 0.80004 ns. Adding this to the delay of the adder gives a total clock delay of 0.910166 ns. So the earliest the schematic clock can switch for subtraction is 0.92 ns.

Reversible full adder gate namely Peres Full Adder Gate (PFAG), the gate is achieved by cascading two 3\*3 Peres gate. The quantum realization cost of this gate is 8 since it includes two 3\*3 Peres gates. The gate can work singly as a reversible full adder circuit when its fourth input is set to zero (D=0). This gate requires only one clock cycle and produces no extra garbage outputs.

Feynman gate. FG also called Controlled-NOT (CNOT) gate, is two input—output reversible gates, with QC equals 1. The relationship between the inputs and outputs are related to and  $Q = A \times B$  When A = 0 then Q = B, when A = 1 then Q = B. The Feynman Gate can be used as a fan-out/copying gate or an XOR gate.

#### III. SIMULATION RESULTS

The implementation and simulation of the proposed algorithm is done over Xilinx 14. The behavioral modeling style and Isim simulator is adopted for simulation. RTL and synthesis results are also generated.

Figure 4: Proposed Top module

| Volume 9, Issue 10, October 2021 |

| DOI: 10.15680/IJIRCCE.2021.0910031 |

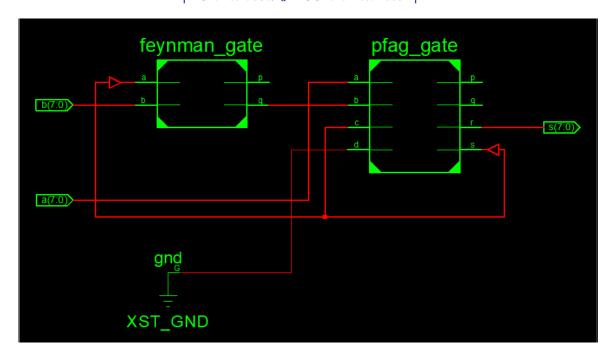

Figure 5: Proposed Reversible circuit using Feynman and Pfag Gate

In figure 5, showing reversible circuit using Feynman and pfag gate in which, Only PFAG has been realized in NMR nanotechnology. The quantum cost of PFAG is 10, It has also been observed that PFAG is better than TSG, MKG and HNG in terms of hardware complexity. It includes 4 PFAG and requires 4 constant inputs. The quantum realization cost of the proposed implementation is 32 and the design produces 10 garbage outputs.

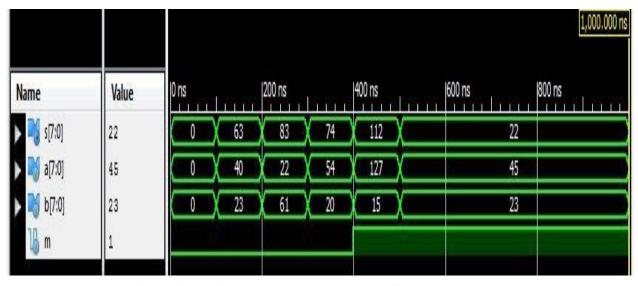

Figure 6: Result in test bench Conventional 8 bit full adder/Subtractor

5

Power consumption

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| www.ijircce.com | | Impact Factor: 7.542

| Volume 9, Issue 10, October 2021 |

| DOI: 10.15680/LJIRCCE.2021.0910031 |

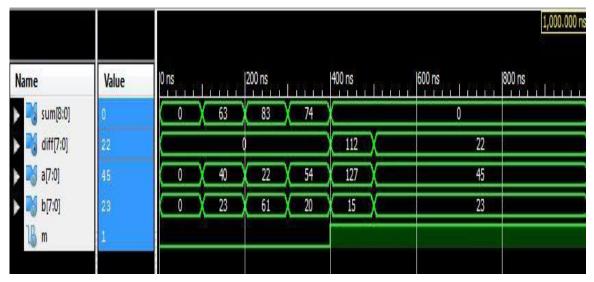

Figure 7: Result in test bench reversible 8 bit full adder/Subtractor

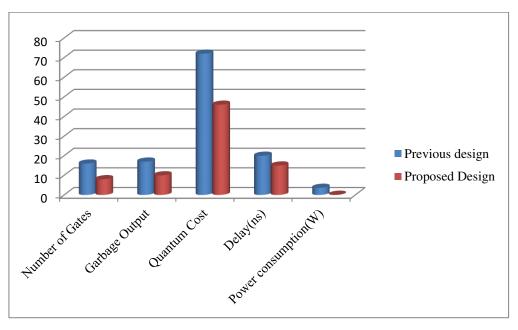

Sr no. Parameter Previous design Proposed Design Number of Gates 1 16 8 2 Garbage Output 17 10 3 72 46 Quantum Cost 4 Delay 20ns 15ns 3.643 W 0.091W

Table 1: Comparison of previous work with proposed work

Figure 8: Comparison of previous and proposed work

The optimization is achieved on some selected factors such as number of gates, garbage outputs and quantum cost as compared to the existing designs. This proposed adder-subtractor circuit is designed using only 8 gates, generates 10 garbage outputs and total quantum cost of the circuit is equal to 46. This adder-subtractor circuit may be utilized in various computational devices for designing low power loss electronic systems.

#### International Journal of Innovative Research in Computer and Communication Engineering

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| www.ijircce.com | | Impact Factor: 7.542

|| Volume 9, Issue 10, October 2021 ||

| DOI: 10.15680/IJIRCCE.2021.0910031 |

#### IV. CONCLUSION

The final entity was then tested by choosing cases which would show what the 8-bit adder/subtractor can successfully add/subtract, and for what values it produces results which are not meaningful. These limitations imposed by the design were outlined. By comparing the output timing diagrams in ModelSim against an arithmetically constructed truth table, finally it is verified the accuracy of our verilog code in correctly representing the 8-bit adder/subtractor network.

#### REFERENCES

- 1. V. Shukla, O. P. Singh, G. R. Mishra and R. K. Tiwari, "Design and performance analysis for the reversible realization of adder/subtractor circuit," 2017 International Conference on Emerging Trends in Computing and Communication Technologies (ICETCCT), Dehradun, 2017, pp. 1-6.

- 2. V. P. Singh and M. Rai, "Reversible adder-subtractor circuit with carry and borrow propagate facility," 2017 3rd International Conference on Advances in Computing, Communication & Automation (ICACCA) (Fall), Dehradun, 2017, pp. 1-6.

- 3. S. S. Kumar and B. Kala, "Performance analysis of modulo 2n+1 subtractor and combined adder/subtractor architectures," 2017 International Conference on Energy, Communication, Data Analytics and Soft Computing (ICECDS), Chennai, 2017, pp. 736-741.

- 4. S. S. Ramachandran and K. J. J. Kumar, "Design of a 1-bit half and full subtractor using a quantum-dot cellular automata (QCA)," 2017 IEEE International Conference on Power, Control, Signals and Instrumentation Engineering (ICPCSI), Chennai, 2017, pp. 2324-2327.

- 5. V. Shukla, O. P. Singh, G. R. Mishra and R. K. Tiwari, "A novel approach for reversible realization of 8-bit addersubtractor circuit with optimized quantum cost," 2016 International Conference on Emerging Trends in Engineering, Technology and Science (ICETETS), Pudukkottai, 2016, pp. 1-6.

- 6. V. Shukla, O. P. Singh, G. R. Mishra and R. K. Tiwari, "Performance parameters optimization and implementation of adder/subtractor circuit using reversible logic approach," *2016 11th International Conference on Industrial and Information Systems (ICIIS)*, Roorkee, 2016, pp. 323-328.

- 7. K. Ghosh, M. M. Haque and S. Chakraborty, "Design of reversible ternary adder/subtractor and encoder/priority encoder circuits," 2016 International Conference on Communication and Signal Processing (ICCSP), Melmaruvathur, 2016, pp. 1290-1295.

- 8. M. Sangsefidi, M. Karimpour and M. Sarayloo, "Efficient Design of a Coplanar Adder/Subtractor in Quantum-Dot Cellular Automata," 2015 IEEE European Modelling Symposium (EMS), Madrid, 2015, pp. 456-461.

- 9. R. Bardhan, T. Sultana and N. J. Lisa, "An efficient design of adder/subtractor circuit using quantum dot cellular automata," 2015 18th International Conference on Computer and Information Technology (ICCIT), Dhaka, 2015, pp. 495-500.

- 10. N. J. Lisa and H. M. H. Babu, "Design of a Compact Ternary Parallel Adder/Subtractor Circuit in Quantum Computing," 2015 IEEE International Symposium on Multiple-Valued Logic, Waterloo, ON, 2015, pp. 36-41.

- 11. A. K. Chowdhury, D. Y. W. Tan, S. L. B. Yew, G. L. C. Wyai, B. Madon and A. Thangarajah, "Design of full adder/subtractor using irreversible IG-A gate," 2015 International Conference on Computer, Communications, and Control Technology (I4CT), Kuching, 2015, pp. 103-107.

- 12. A. Rahman, Abdullah-Al-Kafi, M. Khalid, A. T. M. S. Islam and M. Rahman, "Optimized hardware architecture for implementing IEEE 754 standard double precision floating point adder/subtractor," 2014 17th International Conference on Computer and Information Technology (ICCIT), Dhaka, 2014, pp. 147-152.

### INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN COMPUTER & COMMUNICATION ENGINEERING

📵 9940 572 462 🔯 6381 907 438 🖂 ijircce@gmail.com