(An ISO 3297: 2007 Certified Organization) Website: <u>www.ijircce.com</u> Vol. 5, Issue 4, April 2017

# Urdhwa Multiplier using XOR-XNOR based 4:2 and 7:2 Compressors

### Khushboo Rajani

M. Tech Student, Dept. of E.C., Medicaps Institute of Technology and Management, Indore, India

ABSTRACT: Digital signal processor forms a very important part for any signal processing application.

While designing a processor, high speed processing and low area design are the two key factors of concern in today's era. It is a well-known fact that a multiplier unit forms an integral part of processor design. Due to this regard, high speed multiplier architectures have become the need of the day. In this paper, we have introduced urdhawa multiplier, which is considered to be the fastest multiplier because of its feature of parallel calculation. Also, three designs for Urdhawa Multiplier are further developed and described. In first design, 5:3 compressors based on full adder and utilization in term of 42 delays and 21 areas is developed. In second design we have developed 5:3 compressors based on XOR gate and utilization in term of 36 delays and 24 areas. In third design we have developed 5:3 compressors based on full adder and utilization in term of 28 delays and 18 areas. All the designs and experiments were carried out on Xilinx Vertex-7 series of FPGA and the timing and area of the design on the same have been calculated.

**KEYWORDS**: 4:2 Compressor based on Full Adder, 4:2 Compressor based on XOR Gate, 4:2 Compressor based on XOR-XNOR Gate.

### I. INTRODUCTION

Digital signal processing (DSP) is generally defined as the mathematical manipulation of an information signal to modify, analyse or improve it in a particular way. It can be characterized either by the representation of discrete time, discrete frequency or other discrete domain signals by a sequence of numbers or symbols and the processing of these signals [1].

The main goal of DSP is usually to measure, filter and/or compress continuous real-world analog signals. The first step is usually to convert a signal from an analog to a digital form This is done by sampling and then digitizing it using an analog-to-digital converter (ADC), which in turnconverts the analog signal into a stream of numbers. Often the required output signal is another analog output signal, which requires another digital-to-analog converter (DAC). Though this process is more complex than analog processing and has a discrete value range, the application of computational power to digital signal processing allows many advantages over analog processing in many fields, such as error detection and correction in transmission as well as data compression. DSP algorithms were generally performed on standard computers, as well as on specialized processors called digital signal processor and also on purpose-built hardware such as application-specific integrated circuit (ASICs). Today, there are additional technologies used for digital signal processing that include more powerful general purpose microprocessors, field-programmable gate arrays (FPGAs), digital signal controllers (mostly for industrial apps such as motor control [2-3].

### II. URDHWA MULTIPLIER

Vedic mathematics is considered to be an ancient fast calculation mathematics technique which is taken from historical ancient book of wisdom. It is an ancient Vedic mathematics technique that provides the unique technique of mental calculation with the help of simple rules and principles. Swami Bharati Krishna Tirtha (1884-1960), former Jagadguru Sankaracharya of Puri culled set of 16 Sutras (aphorisms) and 13 Sub - Sutras (corollaries) from the Atharva Veda. He developed methods and techniques for amplifying the principles contained in the formulas and their sub-formulas, and called it Vedic Mathematics. According to him, there has been considerable literature on Mathematics in the Veda-sakhas.

(An ISO 3297: 2007 Certified Organization) Website: <u>www.ijircce.com</u> Vol. 5, Issue 4, April 2017

Vedic mathematics is combined from four Vedas (books of wisdom). It covers explanation of several modern mathematical terms including arithmetic, geometry (plane, co-ordinate), trigonometry, quadratic equations, factorization and even calculus.

#### • 4:2Compressor based on Full Adder

Compressor is generally used generally used instead of other adders to add binary numbers with minimal carry propagation. Compressor is a modern digital circuit used for high speed calculations with minimum gates required in the designing technique. Thus, a compressor becomes an essential tool for fast multiplication and adding technique by keeping an eye on fast processor and lesser area.

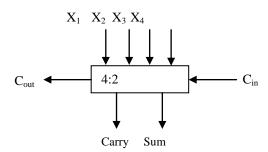

Figure 1: Block Diagram of 5:3 Compressors

4:2 compressors adds 4 bits and one carry, in turn producing a 3 bit output. The 5:3 compressors has 4 inputs  $G_1$ ,  $G_2$ ,  $G_3$  and  $G_4$  and 2 outputs Sum and Carry along with a Carry-in (Cin) and a Carry-out (Cout) as shown in Figure 1. The input Cin, shown in the figure 2 is the output from the previous lower significant compressor.

The Cout, again is the output to the compressor in the next significant stage. The final critical path calculated is smaller in comparison with an equivalent circuit to add 5 bits using full adders and half adders. The basic equation by which 5:3 compressors is governed by the basic equation

$$X_1 + X_2 + X_3 + X_4 + C_{in} = Sum + 2 * (Carry + C_{out}) (1)$$

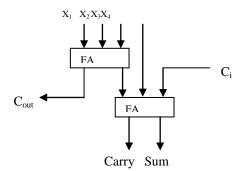

Figure 2: 4:2Compressors based on Full Adder

The standard implementation of the 5:3 compressors is done using 2 Full Adder cells as shown in Figure 2.

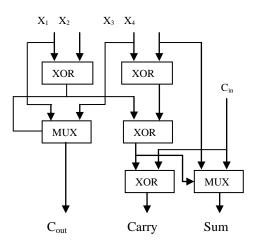

### • 5:3 Compressor based on XOR Gate

Figure 3 shows that 5:3 compressor can also be designed using XOR gates when the individual full adders are broken into their constituent XOR blocks. In general case, it can be observed that the overall delay is equal to 4\*XOR. Figure 3

Copyright to IJIRCCE

(An ISO 3297: 2007 Certified Organization) Website: <u>www.ijircce.com</u> Vol. 5, Issue 4, April 2017

shows the existing architecture for the implementation of the 5:3 compressor resulting with a delay of 3\*XOR. The equations governing the outputs in the existing architecture are shown below

$$Sum = X_1 \oplus X_2 \oplus X_3 \oplus X_4 \oplus C_{in} \qquad (2)$$

Figure 3: 4:2 Compressors based on XOR Gate

$$C_{out} = (X_1 \bigoplus X_2) \cdot X_3 + (\overline{X_1 + X_2}) \cdot X_3 \quad (3)$$

$Carry = (X_1 \oplus X_2 \oplus X_3 \oplus X_4) \cdot C_{in} + (\overline{X_1 \oplus X_2 \oplus X_3 \oplus X_4}) \cdot X_4(4)$

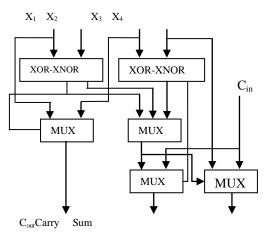

### • Compressor based on XOR Gate

It is observed that replacing some XOR blocks with multiplexer's results in a significant improvement in delay. It is so because the MUX block at the SUM output gets the select bit before the inputs arrive and thus the transistors are already switched by the time they arrive. This minimizes the delay to a considerable extent. This is shown in figure 4.

Figure 4: 4:2 Compressors based on XOR-XNOR Gate

The equations governing the outputs in the proposed architecture are shown below

$Sum = (X_1 \oplus X_2) \cdot (X_3 \oplus X_1) \top (X_1 \oplus X_2) \cdot (X_3 \oplus X_1) \cdot C_{in}$ (5)  $C_{out} = (X_1 \oplus X_2) \cdot X_3 + (\overline{X_1 + X_2}) \cdot X_1$ (6)

Copyright to IJIRCCE

(An ISO 3297: 2007 Certified Organization) Website: <u>www.ijircce.com</u> Vol. 5, Issue 4, April 2017

$Carry = (X_1 \oplus X_2 \oplus X_3 \oplus X_4) \cdot C_{in} + (\overline{X_1 \oplus X_2 \oplus X_3 \oplus X_4}) \cdot X_4(7)$

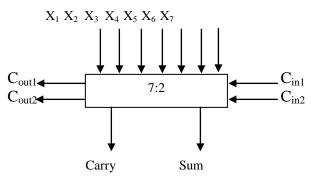

#### • 7:2Compressor

A 7:2 compressors as shown in figure 5, is capable of adding 7 bits of input and 2 carry's from the previous stages, at a time, almost similar to 4:2 compressor which is capable of adding 4 inputs and resulting in 2 outputs.

Figure 5: Block Diagram of 7:2 Compressors

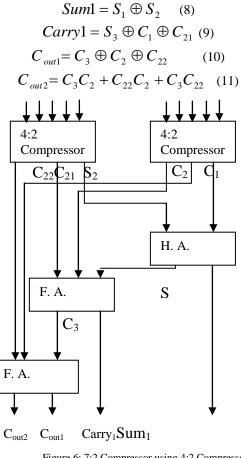

In our implementation, we have designed a novel 9:4 compressor utilizing two 5:3 compressors, two full adders and one half adders. The architecture for the same has been shown in Figure 6.

Figure 6: 7:2 Compressor using 4:2 Compressor DOI: 10.15680/IJIRCCE.2017. 0504337

(An ISO 3297: 2007 Certified Organization) Website: <u>www.ijircce.com</u> Vol. 5, Issue 4, April 2017

### III. DELAY AND AREA EVALUATION METHODOLOGY

As per the delay and area evaluation methodology, all gates to be made up of AND, OR, and Inverter (AOI), each one of them having delay equal to 1 unit and area equal to 1 unit.

| Adder Blocks | Delay | Area |

|--------------|-------|------|

| XOR          | 3     | 5    |

| 2:1 MUX      | 3     | 4    |

| Half Adder   | 3     | 6    |

| Full Adder   | 6     | 13   |

Table 1: Delay and Area Count of the Basic Blocks of Urdhwa Multiplier

We then add up the number of gates in the longest path of a logic block that contributes to the maximum delay. The area evaluation is done by counting the total number of AOI gates required for each logic block.

| Architecture            | No. of Gate | Delay |

|-------------------------|-------------|-------|

|                         | Count       |       |

| 5:3 Compressor based on | 42          | 21    |

| Full Adder              |             |       |

| 9:4 Compressor          | 116         | 57    |

| Compressor based        | 1132        | 591   |

| Urdhwa Multiplier       |             |       |

| 5:3 Compressor based on | 36          | 24    |

| XOR Gate                |             |       |

| Modified 9:4            | 104         | 63    |

| Compressor              |             |       |

| Modified Compressor     | 1012        | 654   |

| based Multiplier        |             |       |

| 5:3 Compressor based on | 28          | 18    |

| XOR-XNOR Gate           |             |       |

| Proposed 7:3            | 88          | 51    |

| Compressor              |             |       |

| Proposed                | 852         | 531   |

| Compressor based        |             |       |

| Multiplier              |             |       |

Table II: Delay and Area Count of the of Urdhwa Multiplier

(An ISO 3297: 2007 Certified Organization) Website: <u>www.ijircce.com</u> Vol. 5, Issue 4, April 2017

#### **IV. SIMULATION RESULT**

We functionally verified each unit presented in this paper including all three 4:2 Compressor, 7:2 Compressor, Compressor based Urdhwa multiplier. We have been found from the results shown in Table 3 respectively, that number of slices used is same in case of 4:2 compressor based on Full adder and 4:2 compressor based on XOR gate which is less than slices used in 4:2 compressor based on XOR-XNOR gate.

| Design            | No. of | No. of 4   | MCPD   |

|-------------------|--------|------------|--------|

|                   | slices | input LUTs | (ns)   |

| Urdhwa Multiplier | 108    | 190        | 25.816 |

| (Full Adder)      |        |            |        |

| Urdhwa Multiplier | 88     | 158        | 21.011 |

| (XOR Gate)        |        |            |        |

| Urdhwa Multiplier | 78     | 143        | 20.951 |

| (XOR-XNOR Gate)   |        |            |        |

Table 3: Device utilization summary (Vertex-4) of Urdhwa multiplier

#### V. CONCLUSION AND FUTURE WORK

Among all three designs, proposed Urdhwa multiplier based on XOR-XNOR gate provides the least amount of Maximum combinational path delay (MCDP). Also, it takes least number of slices i.e. occupy least area among all three design.

#### REFERENCES

- [1] Sushma R. Huddar and Sudhir Rao, Kalpana M., "Novel High SpeedVedic MathematicsMultiplierusingCompressors ", 978-1-4673-5090-7/13/\$31.00 ©2013 IEEE.

- S. S. Kerur, Prakash Narchi, Jayashree C N, Harish M Kittur and Girish V A, "Implementation of Vedic multiplier for Digital Signal Processing", International Conference on VLSI, Communication & Instrumentation (ICVCI) 2011, Proceedings published by International Joural of Computer Applications® (IJCA), pp.1-6.

Himanshu Thapaliyal and M.B Srinivas, "VLSI Implementation of RSA Encryption System Using Ancient Indian Vedic Mathematics", Center for VLSI and Embedded System Technologies, International Institute of Information Technology Hyderabad, India.

- [4] Jagadguru Swami Sri Bharati Krishna Tirthaji Maharaja, "Vedic Mathematics: Sixteen simple Mathematical Formulae from the Veda", Delhi(2011).

- [5] Sumit Vaidya and Depak Dandekar. "Delay-power perfor-mance comparison of multipliers in VLSI circuit design". International Journal of Computer Networks & Communications (IJCNC), Vol.2, No.4, July 2010.

- [6] P. D. Chidgupkar and M. T. Karad, "The Implementation of Vedic Algorithms in Digital Signal Processing", Global J. of Eng. Edu, Vol.8, No.2, 204, UICEE Published in Australia.

- [7] Asmita Haveliya, "Design and Simulation of 32-Point FFT Using Radix-2 Algorithm for FPGA Implementation", Second International Conference on Advanced Computing & Communication Technologies IEEE 2012.

- [8] S. Correa, L. C. Freitas, A. Klautau and J. C. W. A. Costa, "VHDL Implementation of a Flexible and Synthesizable FFT Processor", IEEE LATIN AMERICA TRANSACTIONS, VOL. 10, NO. 1, JAN. 2012.

- [9] Kamaru Adzha Bin Kadiran. "Design and Implementation of OFDM Transmitter and Receiver on FPGA Hardware", November 2005.