e-ISSN: 2320-9801 | p-ISSN: 2320-9798

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN COMPUTER & COMMUNICATION ENGINEERING

Volume 9, Issue 7, July 2021

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

$\odot$

### Impact Factor: 7.542

9940 572 462

6381 907 438

🛛 🖂 ijircce@gmail.com

🙋 www.ijircce.com

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| www.ijircce.com | |Impact Factor: 7.542

|| Volume 9, Issue 7, July 2021 ||

| DOI: 10.15680/IJIRCCE.2021.0907127 |

## Design Implementation and Functional Verification of AMBA Advanced Peripheral bus Protocol using UVM

N B Harshitha, Praveen Kumar Y G, Dr. M Z Kurian, Ravi Hosamani

PG Student [VLSI system design], Dept. of ECE, Sri Siddhartha Institute of Technology, SSAHE,

Tumakuru, India

Asst. Professor, Dept. of ECE, Sri Siddhartha Institute of Technology, SSAHE, Tumakuru, India

Professor and Head, Dept. of ECE, Sri Siddhartha Institute of Technology, SSAHE, Tumakuru, India

Asst. Professor, Dept. of ECE, K. L. E. Institute of Technology, Hubballi, India

**ABSTRACT:** The on-chip bus in system-on-chip implements architecture called Advanced Microcontroller Bus Architecture (AMBA). AMBA is extensively implemented in the Application Specific Integrated circuit (ASIC) and SOC components. Advanced Peripheral Bus (APB) is a low-bandwidth and low-performance bus connected to low bandwidth peripherals like Keypad, UART, timer, etc... For interfacing purposes, low execution transport and fewer data move capacity in APB are used. The paper proposes the design and verification of the APB Protocol. The design is implemented using Verilog HDL and test cases are generated. The verification is carried out using Universal Verification Methodology (UVM). The software used here is Synopsys with technology. A standard methodology for the verification of an Integrated Circuit (IC) design is UVM.UVM Consists of a set of base classes with methods defined in it.

**KEYWORDS:** System-on-chip; Universal Verification Methodology; Bus Architecture; Advanced Peripheral Bus; Universal Verification Methodology; Verilog HDL.

#### I. INTRODUCTION

To overthrow the challenges so far for realizing the opportunities introduced by density and capability of semiconductors, electronic companies employ a SOC design methodology by including the proposed components called as SOC-Intellectual property. SOC is defined as a complex IC which integrates the utmost functional elements into the product forming a single chip. It contains analog, mixed, and digital signal and speed functions all located on a Single substrate [1]. These days in this era of modern technology, more devices are integrated with SOC form. In electronics industry SOC's are very commonly used due to its low power consumption and also embedded system makes great use of it. Some of the advantages of SOC's are low power, low cost, small size, fast operation, and disadvantages are increase in complexity, cost, and more complicated verification.

Reusable IPs fit for the improvisation of an ARM particularly focuses on the crucial of any Application Specific Integrated Circuit (ASIC) configuration. Rather than schematic graphs most of the Interconnections in checked IP squares and blocks depend upon the Hardware Description Language (HDL). They are Register transfer level (RTL) codes which are robust tried in the improvement of SOC.

A SOC principal feature is not only about the components and blocks it comprises but also about the interconnection between them. So, AMBA plays an important role in the interfacing of this block with each other. AMBA is a set of interconnecting specifications given by ARM which standardizes the on-chip communication between different blocks for the construction of High-Performance SOC Design. It is a freely available, platform-independent, open standard for interconnection among the blocks in SOC design and can be implemented with any processor architecture. AMBA usually consists of at least one or more microprocessors or microcontrollers along the internal or external memory bridge, Digital signal processing (DSP), Direct memory access (DMA), and other peripherals such as UART, Keypad, etc all are integrated on a single chip [2]. The primary motivation of AMBA is to have an efficient and standard way for the interconnection of blocks with reuse across multiple designs.

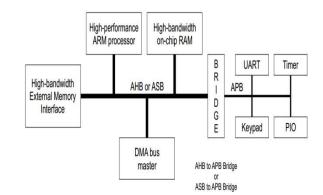

Figure 1 shows AMBA architecture mainly had 3 components, namely advanced system bus, advanced high bus (AHB), APB. The first two protocols are for high bandwidth interconnection and they are high-performance buses. So the higher bandwidth components such as on-chip RAM, DMA bus master, memory interface, and High-performance

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| <u>www.ijircce.com</u> | |Impact Factor: 7.542

Volume 9, Issue 7, July 2021

| DOI: 10.15680/LJIRCCE.2021.0907127 |

ARM processor. The AMBA 3 protocol family includes APB. It is an unpipelined protocol [3]. This paper presents the read and writes transfer without wait states of APB protocol.

Figure 1: AMBA Architecture [4].

Open verification methodology (OVM) derives Universal verification methodology (UVM) which is given by an Accellera standard with EDA tool vendors. It is a standard verification methodology. With the help of UVM, more advanced methods are present in verification technology with the creation of reusable, robust, interoperable verification and test benches [5]. In this paper UVM is used for the verification Due to the For the newly joined and advanced teams in verification technology, UVM addresses the complexity in verification and interplay with companies and all over the electronic industry to provide consistency. Some of the common scripting languages are Python and Perl.

#### II. LITERATURE SURVEY

In an article [6], the APB bridge is implemented in an efficient arrangement of the system schemes are proposed. During the design of any sequential system, the clock becomes the major concern because when there is a generation of difference between the arrival times of clock signal then clock skews are introduced. The author proposes a ripple counter for the reduction of these clock skews.3-bit down ripple counter is implemented using Verilog HDL. An 8-bit APB bridge implementation is done on the Zync board. Vivado Design Suite ISim has been used for simulation and synthesis and design utilization summary Vivado Integrated Design Environment. (IDE) is used.

In the paper [7], APB Convention is implemented with the ASIC design flow has been proposed. The author presents the structure of APB. In APB, the peripherals are interfaced with the help of low data move capacity, low execution transport present. The ASIC execution of the present design is done in a synopsis toolchain with a 32nm library and verified utilizing UVM.

At the end of the paper, the author gives an ASIC design for APB by using Verilog HDL according to their constraints. Here design deals with maintaining the balancing between speed and region overhead. In the results and discussion, the APB simulation result is described. The read-write activity is carried with and without wait states.

In an article [8], the author proposes the IP core of the APB Bridge, which translates the capital AXI4.0-lite transfers into the APB4.0 specifications given by ARM in March 2010. Here the bridge provides the interfaces between the low-power APB domain and high-performance AXI bus. The author concludes that features of the implementation are proven as the PCLK clocked domain and the ALCK domain are completely independent and 32 bit APB master and AXI slave interface are achieved. It supports up to 16 APB peripherals.

In paper [9], the author describes the successful change in the widespread acquisition of system Verilog features for the verification in UVM. System Verilog verification is similar to the UVM verification for some users. This paper discusses the relations between UVM and System Verilog, by the addition of features in system Verilog which made the UVM smaller, easier to understand, and to use. At the end of the paper, It may look like the UVM fills all the drawbacks in the system Verilog but it is not the case with the author. So, according to the author System, Verilog and UVM have their advantages and disadvantages.

In paper [10], the authors present the rapid growth in SOC for the integration of many hardware accelerators into them. The challenges are performance goals, time to market, and functional verification. The author proposes a methodology on the vision-based hardware accelerators of SOC by tracing efficient and rapid ways for verifying their performance. The author concludes by proposing a methodology efficiently and rapidly for the verification of the accelerators. The effective method for the particular is by simulating at low resolution so that it reduces simulation time.

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| <u>www.ijircce.com</u> | |Impact Factor: 7.542

|| Volume 9, Issue 7, July 2021 ||

| DOI: 10.15680/IJIRCCE.2021.0907127 |

#### III. APB DESIGN

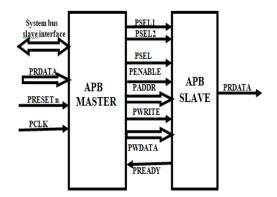

The APB is represented by the AMBA protocol family. It is low bandwidth and a low-cost interface which reduces complexity during interfacing and reduces power consumption [11]. The APB can be interfaced to the peripherals which are low bandwidth such as UART, Keypad, etc. It has an unpipelined protocol thus a high-performance bus interface is not needed. The transition of signals is carried out during the rising edge of the clock for the integration of APB peripherals. From this APB can be implemented into any design flow.APB is a peripheral bus run at a speed of ~100MHZ. For every data transfer, it takes 2 cycles they are – setup cycle, Access cycle.

The APB is represented by the AMBA protocol family. It is low bandwidth and a low-cost interface which reduces complexity during interfacing and reduces power consumption [11]. The APB can be interfaced to the peripherals which are low bandwidth such as UART, Keypad, etc. It has an unpipelined protocol thus a high-performance bus interface is not needed. The transition of signals is carried out during the rising edge of the clock for the integration of APB peripherals. From this APB can be implemented into any design flow.APB is a peripheral bus run at a speed of ~100MHZ. For every data transfer, it takes 2 cycles they are – setup cycle, Access cycle.

Figure 2: APB Block diagram.

| Signal  | Source          | Description                                                                                                 |

|---------|-----------------|-------------------------------------------------------------------------------------------------------------|

| PCLK    | Clock source    | The rising edge of PCLK times.                                                                              |

| PRESET  | System bus      | The reset signal is active low.                                                                             |

| PADDR   | APB bridge      | 32-bit wide bus directed by the bridge unit.                                                                |

| PSELX   | APB bridge      | APB bridge generates this signal for each slave.                                                            |

| PENABLE | APB bridge      | This signal represents the other<br>two cycles after the default<br>cycle.                                  |

| PWRITE  | APB bridge      | When this signal is high it<br>indicates APB write access and<br>when low indicates the APB<br>read access. |

| PWDATA  | APB bridge      | 32-bit wide bus. Directed by bridge during write cycles.                                                    |

| PREADY  | Slave interface | This signal extends APB transfer.                                                                           |

| PRDATA  | Slave interface | 32-bit wide read data. Based on<br>PSEL of slaves this bus is<br>driven during read cycles.                 |

Table 1: List of APB signals.

There are 2 independent data buses present in the APB protocol –Read data and write data are up to 32 bits wide. As there were no individual handshake signals for these buses the data transferring is not possible to occur on both the buses at a time [13].

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| <u>www.ijircce.com</u> | |Impact Factor: 7.542

Volume 9, Issue 7, July 2021

| DOI: 10.15680/IJIRCCE.2021.0907127 |

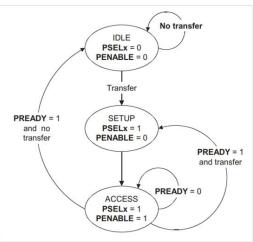

Figure 3: APB state diagram [14].

Figure 3 shows the state diagram of the APB protocol. There are three states, Idle, Setup, and Access states. In Idle state, at first clock cycle, the PSELx and PENABLE are low, there will be no data transfer. When PSELx has asserted the bus waits in the setup state for only one clock cycle. In the next rising edge the PENABLE gets high, the access state gets asserted. During the transition from setup state to access the PWRITE, PSELECT, and write data signals must be stable [15]. If PREADY becomes low then a bus will be in an access state and if it becomes high then it exits from the access state and returns to an idle state.

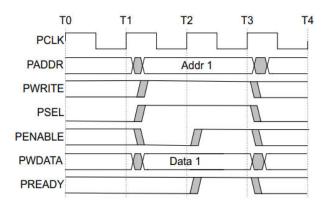

#### A. Write the transfer without wait states

At the first rising edge of the clock cycle, write transfer starts with composing activity with address location (PADDR), data (PWDATA), and signal (PWRITE). The first stage of the clock cycle is the Setup stage/Phase starts with data transfer. During the next edge of the clock cycle, the PENABLE gets asserted and the Access phase takes place [16].

During the access phase all the other control signals, information, locations are kept valid. The transfer ends with the completion of the clock edge during the Access cycle. The PENABLE is low after the completion. If there is no transfer followed by a previous transfer to the same peripheral, then the PSELx goes low.

Figure 4: Without wait states for write transfer.

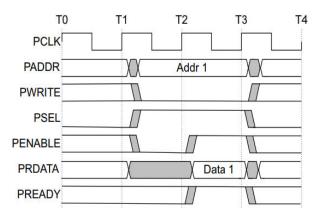

#### **B.** Read transfer without wait states

During the read transfer, the PSEL, PENABLE, PADDR, are kept the same as in the write transfer at the edge of T1 and PWRITE is kept low (setup phase). At T2, PENABLE and PREADY get asserted and read transfer is achieved. Here at the end of the transfer, the slave should provide data.

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| <u>www.ijircce.com</u> | |Impact Factor: 7.542

|| Volume 9, Issue 7, July 2021 ||

| DOI: 10.15680/IJIRCCE.2021.0907127 |

Figure 5: Without wait states for read transfer.

#### **IV. VERIFICATION**

During VLSI design flow, verification plays an important role. This verification helps to realize an error in the RTL design at a prompt stage. So that it won't affect the design process in the belated stage. Utmost 70% of the total time is kept for verification during the process and it is the most time-wasting process. With the rise of the transistors on IC's which causes a reduction in the feature size and use of design tools, the complexity in IC get increases. Hence, the need for the verification of IC is unavoidable.

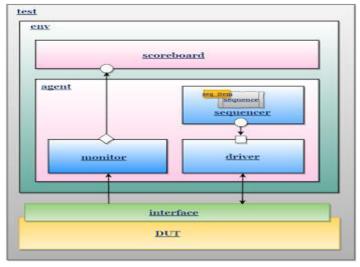

UVM is a standard verification methodology for the verification of the register transfer level structure.UVM has a reusable verification environment i.e. verification components. Base classes of UVM are coded by the System Verilog. These components are encased, configurable, ready to use for protocol interfacing.

Figure 6: UVM Verification environment.

Figure 6 shows the UVM verification environment to verify the APB protocol.

#### A. UVM Testbench

In UVM the top entity is the UVM test. This test is instantiated on the test bench. This test bench instantiates the Design under test (DUT) and UVM test and forms a connection between them. It has Dynamic nature. B. Test

The environment is instantiated in the test. A test can have multiple environments. The test is the top-level component in the UVM test bench.

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| <u>www.ijircce.com</u> | |Impact Factor: 7.542

|| Volume 9, Issue 7, July 2021 ||

| DOI: 10.15680/IJIRCCE.2021.0907127 |

#### C. Environment

UVM environment is a hierarchical component that instantiates all the components they are agent, score board, or other environments are also instantiated in them.

#### D. Sequence Item

Each sequence consists of n number of sequence items. These are the extension from the uvm\_sequence\_item. This unit randomizes the data and address.

#### E. Driver

UVM\_component extends the UVM\_Driver. It communicates through TLM ports. It receives the sequence item transactions from UVM\_sequencer and drives it on the DUT interface.

#### F. Monitor

It is analogous to the driver. It samples the DUT interface and sends it to test bench components. Analysis ports are used for communication.

#### G. Agent

UVM\_Agent is extended from the UVM\_ component. Agent comprises the driver, monitor, and sequencer.

#### H. Scoreboard

This checks the behavior of the DUT. The scoreboard receives the transaction which carries inputs and outputs of DUT through transistor level modeling (TLM).

#### V. RESULTS AND DISCUSSION

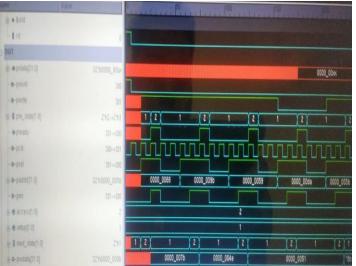

Figure 7 shows the read and write transfer of the data in hexadecimal format. From the simulation waveform, we can see that when the PWRITE is high the APB is writing the data and PWRITE is low APB reads the data

Figure 7: Simulation results after the verification of APB

Figure 8 shows the UVM report summary. The UVM\_INFO shows thirty-five information messages. According to the UVM summary, the design is error-free and there is no more UVM\_WARNING, UVM\_ERROR and UVM\_FATAL are zero.

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| www.ijircce.com | |Impact Factor: 7.542

Volume 9, Issue 7, July 2021

| DOI: 10.15680/IJIRCCE.2021.0907127 |

| Number of denoted UVM.FATAL reports : 0<br>Number of denoted UVM.FATAL reports : 0<br>Number of caught UVM.FATAL reports : 0<br>Number of caught UVM.FATAL reports : 0<br>Number of caught UVM.FATAL Reports : 0<br>UVM_INFO /tools/symcpasys/installers/vcs/etc/uvm-1.2/base/uvm_report_server.svh(901) @ 100145: reporter [UVM/REPORT/SERVER]<br>UVM.Report.summarv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| ** Report counts by severity<br>UVM_INF0 : 35<br>UVM_SERNDA : 0<br>UVM_FERNDA : 5<br>UVM_FERNDA : 0<br>** Report counts by id<br>[] 10<br>[] 40<br>[] 4 |                                                         |

| <pre>sfinish called from file '/tools/synopsys/installers/vcs/etc/uvm-1.2/base/uvm_root.svh*, line 527.<br/>sfinish at simulation time 100145<br/>V C S S in u Lation Report<br/>Time: 100145 ps<br/>CPU Time: 1.030 seconds; Data structure size: 0.6Mb<br/>Sat ul 24 09:17:24 2821<br/>[dvf41sc20@ballash apb_uvml# /simv -gui=dve</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Activate Windows<br>Go to Settings to activate Windows. |

Figure 8: UVM Report summary.

#### **VI.** CONCLUSION

The main aim of the project is to design and verify an APB protocol using UVM. As a prior work to carry out this project, a literature survey has been done. APB protocol design is done for write and read operations without wait states and verification is carried out by using Universal Verification methodology using synopsis in 14nm technology. So, the simulation results show that the data read from the memory location is the same as the data written in that memory location. The UVM summary makes sure the accuracy of the design.

#### References

- 1. Grant Martin, Henry Cheng, "System-on-chip design", Proceedings of 4<sup>th</sup> International Conference on ASIC proceedings, Shanghai, China, PP: 12-17, 2002.

- 2. Ms.Radhika Koti, Ms.Divya Mushram, "An Overview of AMBA relate on APB Bridge", International Journal of Scientific and Research Publication, Volume 03, Issue 04, PP: 12-17, 2013.

- 3. Kommirisetti Bheema Raju, Bala Krishna Konda, "Design and verification of AMBA APB Protocol", International Journal of Engineering Research and Application, Volume 07, Issue 01, PP: 87-90, January 2017.

- Perumalla Giridhar, Dr.Priyanka Choudhury "Design and Verification of AMBA AHB", proceedings of 1<sup>st</sup> International Conference on Advanced technologies in Intelligent control, Environment, Computing, and Communication Engineering, Bangalore, India, PP: 310, 2019.

- 5. Gorwadia Sumit, Mr.Jayesh Popat, "Development of Verification IP for DDR2 memory with performance monitor", International Journal of Advanced Research in Engineering Science and Technology, Volume 04, Issue 05, PP: 80-85, May 2017.

- 6. M Kiran Kumar, Amrita Sajja, Dr. Fazal Noorbasha, "Design and FPGA Implementation of AMBA APB Bridge with Clock Skew Minimization Technique", IOSR Journal of VLSI and Signal Processing, Volume 07, Issue 03, PP: 42-45, June 2017.

- K Swetha reddy, Punna Soujanya, D. Kanthi Sudha, "ASIC Design and Verification of AMBA APB Protocol using UVM", International Journal of Innovative Technology and Exploring Engineering, Volume 09, Issue 09, July 2020.

- 8. Chenghai Mai, Zhijun Liu, Xiaoyue Ma, "Design and Implementation of APB Bridge based on AMBA 4.0", proceedings of International Conference on Consumer Electronics, Communications and Networks, China, PP:193-196, June 2011.

- 9. Jonathan Bromley, "If System Verilog Is So Good, Why Do We Need the UVM?" Sharing responsibilities between libraries and the core language, January 2013.

- 10. Mohammedfasiuddin Khan, Vijay Kumar Kodavalla, Abid Uddin Sameer, "Verification Methodology of Vision-Based Hardware Accelerators in System-on-Chip", proceedings on International Conference on Industry 4.0Technology, Vishwakarma Institute of Technology, Pune, India, PP: 39-45, Febraury 2020.

e-ISSN: 2320-9801, p-ISSN: 2320-9798 www.ijircce.com | Impact Factor: 7.542

|| Volume 9, Issue 7, July 2021 ||

| DOI: 10.15680/IJIRCCE.2021.0907127 |

- 11. Shankar, Dipti Girdhar, Neeraj Kr. Shukla, "Design and verification of AMBA APB Protocol", International Journal of Computer Applications, Volume 95, Issue 21, June 2014.

- Kiran Rawat, Kanika Sahni, Sujata Pandey, "RTL Implementation of AMBA ASB APB Protocol at System on chip level", proceedings of 2<sup>nd</sup> International Conference on Signal Processing and Integrated Networks, India, PP: 927-930, 2015.

- 13. ARM, "AMBA Specification (Rev 2.0)", @ http://www.arm.com.

- 14. Heli Shah, Chinmay Modi, Bhargav Tarpara, "Design and Implementation of Advanced peripheral Bus Protocol", International Journal of Scientific Engineering and Applied Science, Volume 01, Issue 03, PP: 492-497, 2015.

- 15. G Venkat Rao, Pasam Abhigna, J Naveen, S Vineeth Reddy, "Design of AMBA APB Protocol", International Journal of Research in Applied Science and engineering technology, Volume 06, Issue 04, PP: 492-497, 2015.

- 16. ARM, "AMBA Specification (Rev 1.0)", @ http://www.arm.com.

#### BIOGRAPHY

**N B Harshitha** is pursuing a Post Graduate in VLSI and Embedded system student in the Electronics and Communication Department, Sri Siddhartha Institute of Technology, SSAHE, India. Her research interests are VLSI, Design Verification, and RTL Design etc...

**Y G Praveen Kumar** obtained his B.E degree in Electronics and communication Engineering from VTU, Belagavi, Karnataka, India in 2008 and Master of Technology in VLSI and Embedded Systems from the same university in 2010. He has been working as Assistant professor in the department of Electronics and Communication Engineering, Sri Siddhartha Institute of Technology, Tumkur, India for 11 years. He is life member in Indian Society for Technical Education (ISTE). He has authored or Co-authored for more than 25 articles in refereed International Journals and conferences. His research interests are in the area of VLSI System Design, Low Power applications, Digital Design.

**Dr. M. Z. Kurian** is a Professor and HOD in Electronics and Communication Engineering, Sri Siddhartha institute of Technology, SAHE, Tumkur, India.

**Ravi Hosamani** obtained his B.E. degree in Electronics and Communication Engineering In 2006 and Master of Technology from VTU,Belagavi, Karnataka,India, in 2010. He currently working as Assistant Professor in the Department of Electronic and Communication Engineering, K.L.E. Institute of Technology, Hubballi, India. With over 11 years of teaching experience.He is a member of IEEE,ISTE and IEI.He has authored/co-authored articles in referred international and national journal and conference. His research interests are VLSI, Signal processing.

## INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN COMPUTER & COMMUNICATION ENGINEERING

🚺 9940 572 462 应 6381 907 438 🖂 ijircce@gmail.com

www.ijircce.com