(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 4, April 2016

# VHDL Design of Efficient Router Architecture for Network-on-Chip

Pranita S. Muley<sup>1</sup>, Prof. Sanghapal D. Kamble<sup>2</sup>, Mr. S. S. Kemekar<sup>3</sup>

M.Tech IV Sem, P. G. Dept. of Electronics (Communication), S. D. C. E, Wardha, M.S. India.

Assistant Professor, P. G. Dept. of Electronics (Communication), S.D. C. E, Wardha, M.S. India.

Dept. of Instrumentation Engineering, Inox Air Product Ltd., Wardha, M.S. India.

**ABSTRACT:** Network-on-Chip (NoC) is a new research in the direction of communication network into System-on-Chip (SoC). Problems of traditional bus-based SoC can be solved and it will give the better communication requirements for SoC design. Efficient communication between devices of NoC are required, router are used for that. Router is the fundamental component of NoC. Arbiter is the important block of router, so performance of arbiter has an impact on router. In this paper, we have designed NoC router architecture by using dynamic adaptive arbiter. We can observe that the power consumption of NoC router using dynamic adaptive arbiter (DAA) is very low as compared to NoC router using round robin arbiter (RRA) along with high speed.

**KEYWORDS:** System-on-Chip (SoC); Network-on-Chip (NoC); Router; Dynamic Adaptive Arbiter; Round Robin Arbiter.

# I. INTRODUCTION

Conventional bus systems and point-to-point links are used as communication architecture has been proved to be a bottleneck that limits the scalability, reusability and reliability of System-on-Chip (SoC) in future. But these alternatives are not suitable for highly complex systems, so new approaches for intra-chip communication are adopted to achieve high performance in SoCs. Networks-on-chip (NoC) has been proposed as a new communication concept that satisfies requirement of the future SoC [5].

In On-chip interconnection network, NoC provides the technology which having routers that are used to connect processing elements. Through the on-chip network, the communication data of PEs are packetized and transferred. Router is the communication element of NoC, which has the important task of guiding and coordinating the data flow. Performance of NoC is mainly determined by the router and virtual-channel router is a better choice for NoC [4].

Input ports those are with heavy load can be authorized with high priority when they have requests to connect the output port, buffer slots for these heavy load input port will be decreased and the performance of the router can be improved. For this arbiter plays an important role to improve the performance of NoC router [5].

For the design of NoC router, fixed priority arbiter is used, but it has a problem of contention, starvation and head-ofline blocking which degrades the performance of NoC [1].

To solve the problem of contention and starvation, round robin arbiter (RRA) based on fixed priority is used. It gives an equal chance for each input port to access the output port and the starvation problem can be solved. But there is a problem of head-of-line blocking as fixed priority is used. So we have designed NoC router using dynamic adaptive arbiter (DAA) based on round robin mechanism, which can remove these problem. It can also reduce the power consumption of NoC router as it is major issue in designing and give high performance of NoC router.

# **II. SYSTEM DESCRIPTION**

# A. NoC Architecture

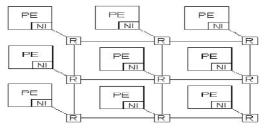

In networking technology to communicate the data within the chip, NoC is used. For transmission of data, all links in NoC can give the high level of parallelism and replace the shared buses or point-to-point dedicated wires

#### (An ISO 3297: 2007 Certified Organization)

#### Vol. 4, Issue 4, April 2016

communication architecture [1]. NoC has advantages of performance, reusability and scalability as compared to traditional bus-based architecture [5]. A typical NoC consists of part as: processing elements (PEs), network interfaces (NIs), and routers. Data is packetizing by NI before using the router backbone to traverse the NoC. To this NI each PE is attached NoC platforms may allow the design productivity to grow as fast as technology capabilities and may eventually close the design productivity gap [2].

Fig. 1 NoC Architecture

#### B. Router Architecture

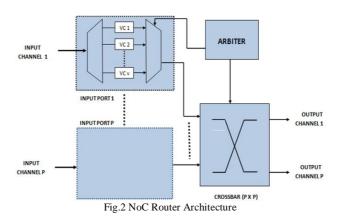

In design of NoC system, router is the key element. The router is used to forward an incoming packet to the destination resource in a packet switched network, either it is directly connected to it, or to forward the packet to another router connected to it. Therefore it is important that design of a NoC router should be simple as possible as implementation cost increases with an increase in the design complexity of a router [4]. The architecture of router is as shown in fig. 2.

It has Virtual channel, Arbiter, Crossbar. Virtual channel is a logical channel which is obtained when physical channel is divided into a multiple number of logical channels. Virtual channels have the advantages of flexibility, better channel utilization and improve network throughput and reduce the effect of blocking [1]. Arbiter receives requests from input buffers and allocates virtual channels according to requests and then gives grant signals to request initiators. It has the updated status of all the ports and which ports are free and also about those ports which are communicating with each other. Consider in a given period of time, there was many input ports that request for the same output or resource, the arbiter process the priorities among many different request inputs. It will release the output port which is connected to the crossbar once the last packet has completed transmission. So that other waiting packets could use the output by the arbitration of arbiter [7].

The arbiter is used to improve the connectivity between the input and output ports and used to determine the implementation sequence of the routing paths so as to solve the problem of conflicting requests of the input ports for the same output port [6]. A crossbar switch (also known as cross-point switch or matrix switch) is a switch which connects multiple inputs to multiple outputs in the form of matrix. The design of crossbar switch has 5 inputs and 5

### (An ISO 3297: 2007 Certified Organization)

#### Vol. 4, Issue 4, April 2016

outputs. On the basis of select lines generated by arbiter, crossbar makes the connections between input port and output port [4]. Input request are granted by the crossbar switch and request data is forwarded to data link, and then through data link, the request data is transmitted to the next hop router [8].

# III. DESIGN OF NoC ROUTER USING ARBITER

NoC router consists of virtual channel, arbiter and crossbar. For high performance of router, design a improving routing algorithm that provides conflict-free paths between input port and output port and require efficient arbiter that authorizes the requiring input port based on good scheduling mechanism. So it plays vital role in the design of NoC router. We have designed NoC router using round robin arbiter (RRA) based on fixed priority and dynamic adaptive arbiter (DAA) based on round robin mechanism to improve total NoC router performance.

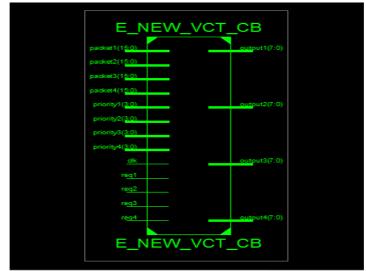

## A. Design of NoC Router Using RRA

This design of NoC router is using round robin arbiter based on fixed priority. In this arbiter, round robin arbitration algorithm is used. A round robin arbiter has the basic concept of operation that request which was just severed should have the lowest priority on the next round of arbitration [7]. Fig. 3 shows the block diagram of the round robin arbiters. It has two barrel shifters, one simple arbiter and one shifter pointer coder [5].

Fig. 3 RTL View of NoC Router Using RRA

As one input port is allowed to access the output port, contention is removed. High degree of fairness is given by arbiter with the agents by treating each input port fairly and guaranteeing fairness in scheduling. Because of that each input port gives an equal chance to access the output port and the starvation problem can be solved [1]. It has a problem of head-of-line blocking as fixed priority is used. This arbiter may degrade the efficiency for some input ports. It is a somewhat time-consuming and is mainly contributed by the input selector to grant the requests, which also finds critical path delay.

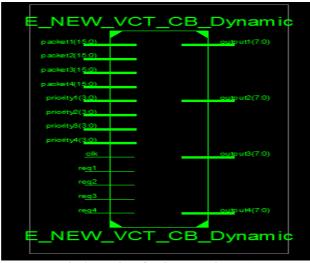

### B. Design of NoC Router Using DAA

The design of NoC router is using DAA. It uses round robin mechanism for its operation. It can change the priority of input port dynamically as per the status of buffer. The input port having highest priority signal is assigned when the buffer signal is full. This input port occupies the desired output port, so buffer pressure of the input port is decreased and therefore the NoC performance can be improved. To remove the problem of starvation for low priority, it works on the concept of round robin mechanism, counter and comparator are also used. The counter is used to keep the record of

#### Copyright to IJIRCCE

(An ISO 3297: 2007 Certified Organization)

## Vol. 4, Issue 4, April 2016

the number of controlling times for high priority input ports. If there is a chance of contention, arbiter determines the output sequence. Arbitration mechanisms allow only one input port to access the output port, so contention is removed. As per the buffer status of the input port, a dynamic priority is assigned for each input. So the problem of head-of-line blocking can be solved.

Fig. 4 RTL view of NoC Router Using DAA

The NoC router using RRA is simulated as shown in fig. 5. RRA is based on fixed priority and highest priority is assigned to port 3. So the output port 3 is enabled.

Fig. 5 Simulation Waveform of NoC Router Using RRA

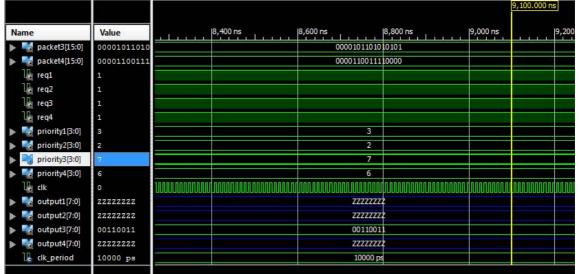

In fig. 6, simulation of NoC router using DAA is shown. DAA is based on round robin mechanism and change the priority dynamically as per the status of buffer. The port 3 is assigned with highest priority, so the output port 3 is enabled to access the input data.

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 4, April 2016

|         |               |             | 966.667 ns      |      |                  |          |          |           |     |

|---------|---------------|-------------|-----------------|------|------------------|----------|----------|-----------|-----|

| Name    |               | Value       | 800 ns          |      | 1,000 ns         | 1,200 ns |          | 1,400 ns  | .1  |

| 🕨 🙆 pa  | acket3[15:0]  | 00001011010 |                 |      |                  | 00001011 | 01010101 |           |     |

| 🕨 📑 ра  | acket4[15:0]  | 00001100111 |                 |      |                  | 00001100 | 11110000 |           |     |

| 🕞 re    | ql            | 1           | 2               |      |                  |          |          |           |     |

| lle re  | iq2           | 1           |                 |      |                  |          |          |           |     |

| 💿 re    | !q3           | 1           |                 |      |                  |          |          |           |     |

| la re   | :q4           | 1           |                 |      |                  |          |          |           |     |

| 🕨 🐻 pi  | riority1[3:0] | 0011        |                 |      |                  | 00       | 11       |           |     |

| ▶ 16 pi | riority2[3:0] | 0010        |                 |      |                  | 00       | 10       |           |     |

| 🕨 🐻 pi  | riority3[3:0] | 0111        |                 |      |                  | 01       | 11       |           |     |

| 🕨 🚟 рі  | riority4[3:0] | 0110        |                 |      |                  | 01       | .10      |           |     |

| 🧔 d     | k             | 1           |                 |      |                  |          |          |           |     |

| ► =6 o  | utput1[7:0]   | 22222222    | Z. 0 ( ZZ       | ZZZ  |                  | 200      | 22222222 |           | ZZ  |

| Þ 6 0   | utput2[7:0]   | 22222222    | ZZZZZ X         | ZZZZ | ZZZZ ) () ( ZZZZ | ZZZZ ) ( | 222222   | 22 0 2222 | 222 |

| ► =6 o  | utput3[7:0]   | 00110011    |                 |      | 00000            | 000      | 200      | 00000     |     |

| Þ 6 0   | utput4[7:0]   | 22222222    | $\sim 0 \sim 0$ |      |                  |          |          | 0000      |     |

| La d    | k_period      | 10000 ps    |                 |      |                  | 1000     | 00 ps    |           |     |

Fig. 6 Simulation Waveform of NoC Router Using DAA

The comparison of Table 1, NoC router using RRA and DAA is as shown. It shows the comparison of result parameters for NoC router using RRA and DAA.

| Parameter            | Power  | Delay   | Resources |              |      |

|----------------------|--------|---------|-----------|--------------|------|

| NoC Router using RRA | 920µW  | 3.683ns | Slice     | Flip<br>Flop | LUTs |

|                      |        |         | 123       | 40           | 224  |

| NoC Router using DAA | 110 μW | 3.683ns | Slice     | Flip<br>Flop | LUTs |

|                      |        |         | 511       | 169          | 976  |

Table 1. Comparison of NoC Router using RRA & DAA

# **V. CONCLUSION**

An efficient and high speed arbiter is needed for high performance of NoC router. The power consumption is also a critical issue for design of NoC router. In this paper, we have designed NoC router using RRA based on fixed priority and DAA based on round robin mechanism. NoC router using RRA having a problem of head-of-line blocking. So NoC router using DAA is used to solve the problem by changing the priority of input port dynamically as per the status of buffer. This decreases the number of buffer slots of the input port and it also reduced the power consumption. So using DAA, we observed that power consumption is very low as compared to NoC router using RRA along with high speed.

## REFERENCES

- 1.

Design of NoC Router Architecture using VHDL Minakshi M. Wanjari Electronics Engineering Dept. PCE Nagpur, India Pankaj Agrawal

Electronics and Comm. Engineering. Dept. RCOEM Nagpur, India R. V. Kshirsagar Electronics Engineering Dept. PCE Nagpur.

- 2. Design And Analysis Of Five Port router For Network On Chip Swapna S Department of Electronics and Communication Engineering, National Institute of Technology, Rourkela, Odisha Ayas Kanta Swain Department of Electronics and Communication Engineering, National Institute of Technology, Rourkela, Odisha Kamala Kanta Mahapatra Department of Electronics and Communication Engineering, National Institute of Technology, Rourkela.

- 3. Review on Network on Chip Router Design V. A. Bute, D.S. Chaudhari E&TC, GCOEA, Amravati, 2 E&TC, GCOEA, Amravati Maharashtra, India.

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 4, April 2016

- Design and Analysis of On-Chip Router for Network on ChipAnuprita.S. Kale, Prof. M. A. Gaikwad Electronics Department, Bapurao Deshmukh college, of engineering, Wardha M. S. India. Professor, Electronics Department, Bapurao Deshmukh college of engineering, Wardha M.S India.

- 5. A dynamic adaptive arbiter for Network-on-Chip Yanhua Liu1, 2, Jie Jin2, 3, Zongsheng Lai11Institute of Microelectronics Circuit & System, East China Normal University, Shanghai, China 2Jiangsu Provincial Key Lab of ASIC Design, Nantong University, Nantong, China 3Shanghai Advanced Research Institute, Chinese Academy of Sciences, Shanghai, China.

- 6. Problems Encountered in Various Arbitration Techniques Used in NOC Router: A Survey Kunj Jain, Sandeep K Singh, Alak Majumder, Abir J Mondal3 1B-Tech Final Year, Department of ECE, NIT Arunachal Pradesh, Yupia, India 791112 2M-Tech Final Year, Department of CSE, NIT Arunachal Pradesh, Yupia, India 791112 3Assistant Professor, Department of ECE, NIT Arunachal Pradesh, Yupia, India 791112 3Assistant Professor, Department of ECE, NIT Arunachal Pradesh, Yupia, India 791112 3Assistant Professor, Department of ECE, NIT Arunachal Pradesh, Yupia, India 791112 3Assistant Professor, Department of ECE, NIT Arunachal Pradesh, Yupia, India 791112 3Assistant Professor, Department of ECE, NIT Arunachal Pradesh, Yupia, India 791112 3Assistant Professor, Department of ECE, NIT Arunachal Pradesh, Yupia, India 791112 3Assistant Professor, Department of ECE, NIT Arunachal Pradesh, Yupia, India 791112 3Assistant Professor, Department of ECE, NIT Arunachal Pradesh, Yupia, India 791112 3Assistant Professor, Department of ECE, NIT Arunachal Pradesh, Yupia, India 791112 3Assistant Professor, Department of ECE, NIT Arunachal Pradesh, Yupia, India 791112 3Assistant Professor, Department of ECE, NIT Arunachal Pradesh, Yupia, India 791112 3Assistant Professor, Department of ECE, NIT Arunachal Pradesh, Yupia, India 791112 3Assistant Professor, Department of ECE, NIT Arunachal Pradesh, Yupia, India 791112 3Assistant Professor, Department of ECE, NIT Arunachal Pradesh, Yupia, India 791112 3Assistant Professor, Department of ECE, NIT Arunachal Pradesh, Yupia, India 791112 3Assistant Professor, Department of ECE, NIT Arunachal Pradesh, Yupia, India 791112 3Assistant Professor, Patrice Pradesh, Yupia, Ind

- Yupia, India. W. J. Dally, "Virtual-channel flow control," IEEE Trans. Parallel Distrib. Syst., vol. 3, no. 2 Mar.1992, pp. 194–205.

A.S. Kale and M. A. Gaikwad, Design and Analysis of On-Chip Router for Network On Chip, International Journal of Computer Trends and Technology, vol. 9, no. 6, pp. 182-186, 2011.

- 8. An Innovative Power-Efficient Architecture for Input Buffer of Network on Chip, Kun Huang Jun Wang Ge Zhang, Key Laboratory of Computer System and Architecture, Institute of Computing Technology, Chinese Academy of Sciences, Beijingss.

- 9. Zero-Efficient Buffer Design for Reliable Network-on-Chip in Tiled Chip-Multi-Processor, Jun Wang1, Hongbo Zeng1, Kun Huang1, Ge Zhang1, Yan Tang, Institute of Computing Technology, Chinese Academy of Sciences; The Ohio State University, wangjun.

- 10. Energy-Efficient Input Buffer Design using Data-Transition Oriented Model Jun Wang, Kun Huang, Ge Zhang, Weiwu Hu, Feng Zhang Key Laboratory of Computer System and Architecture, ICT, CAS, Beijing, 100080, China.

- 11. W. J. Dally and B. Towles, Route packets, not wires: On-chip interconnection networks, in DAC '01: Proceedings of the 38th Conference on Design Automation, Jun. 2001, pp. 684–689.

- 12. J. Kim, D. Park, T. Theocharides, N. Vijaykrishnan and C. R. Das, A low latency router supporting adaptivity for on-chip interconnects, in Proceedings of the 42nd annual Design Automation Conference, .ACM: New York, USA, 2005.

- 13. W. J. Dally, Virtual-channel flow control, IEEE Trans. Parallel Distrib. Syst., vol. 3, no. 2, Mar. 1992, pp. 194–205.

- 14. J. Suseela and V. Muthukumar, Loopback Virtual Channel Router Architecture for Network on Chip, in Proceedings of the Ninth International Conference on Information Technology- New Generations. Apr. 2012, pp. 534 – 539.

- 15. W J. Dally, B. Towels, Principles and Practices of Interconnection Networks, Morgan Kaufmann Publishers Inc, 2003, pp. 305-324.

- T. Bjerregaard, J. Sparso, A router architecture for connection oriented service guarantees in the MANGO clock less network-on chip, in Proceeding of the conference on Design, Automation and Test in Europe, IEEE Computer Society, 2005, pp. 1226-1231.

- 17. L. Benini, G. De Michel, Networks on Chips: A NewSoC Paradigm. Computer, Vol. 35, no.1, Jan.2002, pp.70-78.

- 18. V. Soteriou, R. S. Ramanujam, B. Lin, Li-Shiuan Peh. A High-Throughput Distributed Shared-Buffer NoC Router. IEEE Computer

- Architecture Letters, vol. 8, no. 1, pp. 21-24, Jan.-June 2009, doi: 10.1109/LCA. 2009.5.

- 19. A. Louri, J. Wang, Design of energy-efficient channel buffers withrouter bypassing for network-on-chips (NoCs).