(An ISO 3297: 2007 Certified Organization) Vol. 4, Issue 11, November 2016

# Low Power Hybrid Full Adder Using Transmission Gates

Triveni Vanacharla<sup>1</sup>, Jhansi Rani<sup>2</sup>

M. Tech Student (VLSI), Dept. of Electronics and Communication Engineering, University College of Engineering

Kakinada, Kakinada, Andhra Pradesh, India

Assistant Professor, Dept. of Electronics and Communication Engineering, University College of Engineering

Kakinada, Kakinada, Andhra Pradesh, India

**ABSTRACT:** Addition is a fundamental operation for all the arithmetic operations; it is mainly used in digital signal processing architecture and microprocessor. The sum module is a core of arithmetic operation like addition, subtraction, multiplication and division. The aim of this project is to design a full adder having low power consumption and delay. Here, a new hybrid 1-bit full adder is designed using both CMOS (Complementary metal oxide semiconductor) logic and transmission gate logic for the purpose of reducing the number of transistors. This design was implemented for 1-bit and then extended for 32-bit. This circuit is implemented using Synopsis tools in 35-nm technology. In comparison with existing full adder designs, the present implementation is improved in terms of power and area.

KEYWORDS: CMOS logic, high speed, hybrid design, low power, Transmission-gate.

#### I. INTRODUCTION

The process of creating thousands of transistors are combined to a single integrated chip is a very large scale integration. Using low power components with low power design is more valuable. Full adders Full adders, being one of the most fundamental building block of all the aforementioned circuit applications, remain a key focus domain of the researchers over the years [1], [2]. Different logic styles, each having its own merits and bottlenecks, was investigated to implement 1-bit full adder cells [3]. The designs are classified into two categories static style and dynamic style. Static full adders are more reliable with less power but on chip area is large compared to dynamic style.

Different logic styles tend to favor one performance aspect at the expense of others. Standard static complementary metal–oxide–semiconductor (CMOS) [3], dynamic CMOS logic [4], complementary pass-transistor logic (CPL) [5], [6], and transmission gate full adder (TGA) [7], [8] are the most important logic design styles in the conventional domain. Hybrid technologies are used for designing the full adders in more than one different style. This improvement in power, delay and layout area was obtained using this logic style.

## **II. LITERATURE SURVEY**

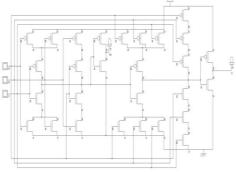

Fig(1): Full Adder using CMOS transistors

(An ISO 3297: 2007 Certified Organization)

#### Vol. 4, Issue 11, November 2016

The advantages of standard complementary (CMOS) style-based adders (with 28 transistors) are its robustness against voltage scaling and transistor sizing; while the disadvantages are high input capacitance and requirement of buffers [3].

#### III. PROPOSED FULL ADDER

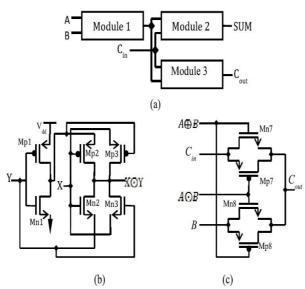

Fig(2): (a) Schematic structure of proposed full adder (b) XNOR module (c) carry generation module

The proposed full adder is represented by three modules as shown in fig(a). Module 1 and Module 2 are the XNOR modules that generates sum signal (SUM) and Module 3 generates the output carry signal ( $C_{out}$ ). XNOR module is responsible for most of the power consumption of the entire adder circuit. Therefore, this module is designed to minimize the power to the best possible extend with avoiding the voltage degradation possibility. The deliberate use of strong transmission gates (channel width of transistors Mn7, Mp7, Mn8, and Mp8 is made large) guaranteed further reduction in propagation delay of the carry signal.

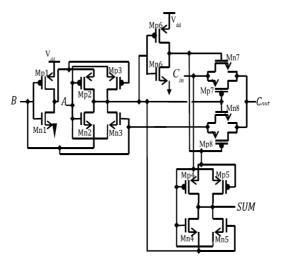

Fig(3): Detailed circuit diagram for proposed full adder

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 11, November 2016

The inverter is formed using transistors Mp1 and Mn1 generate signal B, which is used to implement the controlled inverter using the transistor pair Mp2 and Mn2. Output of this inverter is XNOR of A and B. It has voltage degradation problem which is eliminated using two pass transistors Mp3 and Mn3. PMOS (Mp4, Mp5, Mp6) transistors and NMOS (Mn4, Mn5, Mn6) transistors are form the second stage XNOR module to realize the complete sum function. In this circuit the output carry signal is implemented by the transistors Mp7, Mp8, Mn7 and Mn8. The input carry signal propagates through a transmission gate (Mp7 and Mn7), in order to reduce the overall carry propagation path significantly. The use of these gates are responsible for reduction in propagation delay of the carry signal.

The given hybrid adder requires only 16 transistors whereas the other hybrid adders require more than 20 transistors. By analyzing the truth table of a full adder, the condition for  $C_{out}$  is:

If A=B, then C<sub>out</sub>=B else C<sub>out</sub>=C<sub>in</sub>

### IV. PERFORMANCE OF CARRY LOOK AHEAD ADDER USING TRANSMISSION GATES

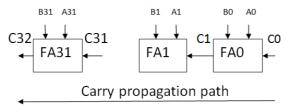

Fig (4) 32 bit carry propagation adder using hybrid adder design

A 32-bit carry propagation adder [fig(4)] is implemented as an extension of the hybrid full adder. It is a non carry look-ahead adder structure where the carry propagation takes place to all the way to the last adder block. Here both the power consumption as well as carry propagation was also improved. The power obtained for this adder is 1.06e-04

#### V. EXPERIMENTAL RESULT

CMOS 28T full adder, hybrid full adder have been successfully implanted using h-spice in synopsis tool. A 35-nm technology libraries is used in this tool. The results are obtained as follows:

Fig(5) Output waveform for hybrid full adder circuit

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 11, November 2016

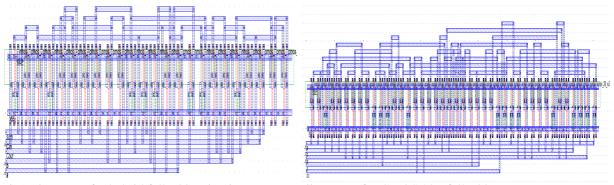

ii. Layout for CMOS 28T full adder

The figures fig(6), (i) and (ii) shows the layout of a proposed full adder and existing full adder respectively. The number of transistors for the proposed hybrid full adder is 16 and the existing full adder is 28. Hence, by observing the layouts of these adders area will be decreased. With an aim to optimize power of the circuit, the energy consumption has been minimized in the proposed case. It was observed that in the present design the power consumption could be minimized by mainly sizing the transistors in inverter circuits, while the carry propagation delay could be improved by mainly sizing the transistors of the transmission gates paths between  $C_{in}$  and  $C_{out}$ . The proposed hybrid adder requires 16 transistors. The use of less number of transistors in this paper also improves speed. The power comparison for different logics has been showed in Table(1).

| Designs                        | Power     | No. of transistors |

|--------------------------------|-----------|--------------------|

| CMOS                           | 7.5e-04   | 28                 |

| CPL                            | 1.759µ    | 32                 |

| HPSC                           | 1.56µ     | 22                 |

| TGA                            | 1.76µ     | 20                 |

| FA HYBRID<br>TGL<br>(Proposed) | 6.864e-05 | 16                 |

Table (1): power comparisons for adders

#### VI. CONCLUSION AND FUTURE WORK

Full adder is used in digital signal processors (DSP) and microprocessor. There is also an increasing demand for mobile electronic devices such as cellular phones, PDA's and laptop computers. In this paper, a low power hybrid full adder has been proposed the design has been extended for 32 bit carry look ahead adder also. The simulation was carried out using synopsis tools with 35-nm technology and compared with CMOS design. By using this hybrid logic

(An ISO 3297: 2007 Certified Organization)

#### Vol. 4, Issue 11, November 2016

design, power is reduced. This paper can be further implemented with pass transistor logic for better power performance.

#### REFERENCES

- 1. Partha Bhattacharyya, Bijoy Kundu, Sovan Ghosh, Vinay Kumar, and Anup Dandapat, "Performance Analysis of a Low-Power High-Speed Hybrid 1-bit Full Adder Circuit" in *proc* IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 23, NO. 10, OCTOBER 2015

- C.-K. Tung, Y.-C. Hung, S.-H. Shieh, and G.-S. Huang, "A low-power high-speed hybrid CMOS full adder for embedded system," in *Proc. IEEE Conf. Design Diagnostics Electron. Circuits Syst.*, vol. 13. Apr. 2007, pp. 1–4.

- 3. S. Goel, A. Kumar, and M. A. Bayoumi, "Design of robust, energyefficient full adders for deep-submicrometer design using hybrid-CMOS logic style," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 14, no. 12, pp. 1309–1321, Dec. 2006.

- 4. N. H. E. Weste, D. Harris, and A. Banerjee, CMOS VLSI Design: A Circuits and Systems Perspective, 3rd ed. Delhi, India: Pearson Education, 2006.

- 5. J. M. Rabaey, A. Chandrakasan, and B. Nikolic, *Digital Integrated Circuits: A Design Perspective*, 2nd ed. Delhi, India: Pearson Education, 2003.

- 6. D. Radhakrishnan, "Low-voltage low-power CMOS full adder," *IEE Proc.-Circuits Devices Syst.*, vol. 148, no. 1, pp. 19–24, Feb. 2001.

- 7. R. Zimmermann and W. Fichtner, "Low-power logic styles: CMOS versus pass-transistor logic," *IEEE J. Solid-State Circuits*, vol. 32, no. 7, pp. 1079–1090, Jul. 1997.

- C. H. Chang, J. M. Gu, and M. Zhang, "A review of 0.18-μm full adder performances for tree structured arithmetic circuits," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 13, no. 6, pp. 686–695, Jun. 2005.

#### BIOGRAPHY

**Triveni Vanacharla** is a student of VLSI technology in the Electronics and Communication Engineering department, University College of Engineering Kakinada. She received bachelors degree in 2012 from VSL Engineering college, Matlapalem, India. Her research interest are low power, physical design etc.

**K. Jhansi rani** is assistant professor in the Electronics and Communication Engineering department, University College of Engineering Kakinada. She received Masters from KITS, Warangal, India. She is a member in IETE. Her research interests are Communication, VLSI, Image processing.