(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 8, August 2016

# A Review on VLSI based DSRC application of FM0/Manchester encoder-decoder

Neeraj Soni<sup>1</sup>, Aman Saraf<sup>2</sup>

P. G. Scholar, Dept. of Electronics and Communication, RITS, RGPV University, Ratibad Bhopal, India<sup>1</sup>

Assistant Professor, Dept. of Electronics and Communication, RITS, RGPV University, Ratibad Bhopal, India<sup>2</sup>

**ABSTRACT:** In the communication system the secure data transmission is very important. Numbers of encoding techniques are used for the communication of data. Several types of applications such as FMO, miller and Manchester encoding are used for the communication which provides the security to the data. These techniques have their own importance that depends on its application and their needs. These techniques are very strong as they provide the result without losing their parameters. Generally these encoding techniques provide the output using FSM (finite state machine) at high speed. Architecture of FMO, Manchester and miller encoding are used to balance the DC output. This is the main advantage of using these techniques. There architecture requires reduced number of the transistors in the design implementation. In this paper a brief review on is presented on VLSI based DSRC (dedicated short-range communication) application of FMO/Manchester encoder-decoder.

KEYWORDS: DSRC, FM0 encoder, FPGA, VLSI, Manchester encoder, SOLS.

### I. INTRODUCTION

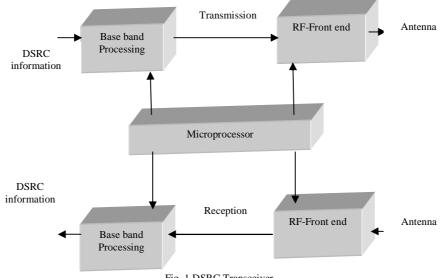

Encoding technique is used in the communication system to convert the information of data into the suitable form of transmission. Encoding techniques are used for the purpose of security. Different encoding techniques used for the serial communication application. The several types of applications such as FMO, Manchester encoding, Miller encoding, NRZ, FM1, RZ, etc. are used for encoding the data. These encoding techniques can also be used in the optical communication; it minimizes the critical area and path-delay by adding buffers in the path of the signals. A baseband processor consists of a PIE reader, UHF/RFID Reader and a decoder (FMO or Miller or other) for encoding and decoding purpose application at a high frequency clock. The architecture system of DSRC transceiver is as shown in Fig 1.

(An ISO 3297: 2007 Certified Organization)

#### Vol. 4, Issue 8, August 2016

The architecture system of dedicated short range communication (DSRC) transceiver is shown in Figure 1. The upper part dedicated for transmission and bottom parts are dedicated for receiving the information. The transceiver is classified into three modules: baseband processing, microprocessor, and RF front-end. The instructions of microprocessor interpret to schedule the tasks of baseband processing and RF front-end from media access control. The baseband processing is dependable for the error correction, modulation, and encoding and clock synchronization. The RF front-end transmits and receives the wireless signal through the antenna.

#### II. RELATED WORK

In [1], [5] author proposed fully reused VLSI (Very Large Scale Integration) architecture by using SOLS technique for both the FM0 and Manchester encoding. The SOLS technique eliminates the limitations of hardware utilization by using two core techniques- (1) Area compact retiming and (2) Balance logic-operation sharing techniques. The Area-compact retiming is used to reduce the hardware problem like number of transistors and the balance logic operation sharing the help identical logic components can be efficiently combines with the FM0 and Manchester encoding. In this paper the proposed method works on parameters like low power consumption, high operating frequency etc. This paper develops a fully reused VLSI architecture and also exhibits a competitive performance compared with the existing works.

In [2], it is shown that an unbalance computation time results in the glitch at the input of MUX that causes the logicfault on coding. This paper overcomes the problem of glitches by using XNOR with the inverter by replacing the XOR and this becomes the input of the MUX. This is done to balance the computational time. The adoption of FM0 or Manchester code depends on Mode and CLR signal. In this design both modes are separately allocated to system controller. Whether FM0 or Manchester code is adopted, all the logic component of the proposed VLSI architecture is utilized and provides better results. The work in [3] presents a review on Manchester, Miller and FM0 encoding techniques. This paper presents the circuit design strategies of Manchester, Miller and FM0 using a finite state machine. A comparative study of all these techniques is also presented in this work.

A review on theoretical background of FM0 and Manchester [4] is presented describing the utility of FM0 and Manchester encoding and how it can be used for DSRC. In DSRC DC-Stability and signal reliability are fulfilled by FM0 and Manchester. These works presents a system of VLSI architecture of FMO/ Manchester encoding using SOLC technique and also compare this technique with other techniques. The SOLS consists of two core methods such as area-compact retiming and balance logic-operation sharing. The area-compact retiming technique relocates the hardware resource to reduce transistors. The balance logic operation sharing technique of SOLC efficiently combines FM0 and Manchester encodings with the fully reused hardware architecture. This paper not only implements a fully reused VLSI architecture, but also exhibits a competitive performance compared with the existing techniques. In [6] presents a review on evaluation of various forms of DSRC system. DSRC is the only short-range wireless alternative today that provides Fast Network Acquisition, Low Latency, High Reliability when Required, Priority for Safety Applications, Interoperability, Security and Privacy which is one of the challenging task faced by all in the worldwide. This article deals with active Dedicated Short Range Communications (DSRC) application for Intelligent Transport Systems (ITS) and its economic evaluation focused on many wireless systems like vehicle communication, mobile Communication etc.

In [7] proposed a fully reused VLSI architecture using the SOLS technique for both FM0 and Manchester encoding. The SOLS technique eliminates the limitation of hardware utilization by two core techniques: area compact retiming and balance logic-operation sharing. The SOLS technique improves the hardware utilization rate from 57.14% to 100% for both FM0 and Manchester encodings. The performance of this paper is evaluated on the post layout simulation in Taiwan Semiconductor Manufacturing Company (TSMC) 0.18- $\mu$ m 1P6M CMOS technology. The maximum operation frequency is 2 GHz and 900 MHz for Manchester and FM0 encodings, respectively. The power consumption is 1.58 mW at 2 GHz for Manchester encoding and 1.14 mW at 900 MHz for FM0 encoding. The core circuit area is 65.98×30.43  $\mu$ m2. This paper not only develops a fully reused VLSI architecture and also exhibits an efficient performance compared with the existing works.

In [8] proposed a fully reused VLSI architecture using SOLS technique for both FM0 and Manchester encodings. The coding diversity between FM0, Manchester and Miller encodings causes the limitation on hardware utilization of VLSI architecture design. The area compact retiming and balance logic operation sharing techniques eliminates the limitation of hardware utilization. Area compact retiming concept relocates the hardware resource and reduced the

#### (An ISO 3297: 2007 Certified Organization)

#### Vol. 4, Issue 8, August 2016

number of transistors effectively. The Balance Logic operation sharing technique combines FM0 and Manchester encodings with the identical logic components to produce balanced computation time. Every component is active in both FM0 and Manchester encodings and it will greatly improve the hardware utilization rate to 100% and reduce the power consumption. The FM0 and Manchester encoders are designed with these techniques to achieve high speed and fully reconfigured VLSI architecture for application system. In future the design can be implemented using high performance FPGA devices.

In [9] proposed a system to minimize the problem of coding-diversity between FM0 and Manchester encodings that causes the limitation on hardware utilization of VLSI architecture design. In this paper, the fully reused VLSI architecture using SOLS technique for both FM0 and Manchester encodings is proposed. Area compact retiming and balance logic operation sharing are the two core techniques that are used to eliminate the limitation on hardware utilization by reducing the number of transistor and by combining the resources of FM0 and Manchester encodings. This paper is realized in 180nm technology with outstanding device efficiency. The power Consumption is 29392.843nW for Manchester encoding and FM0 encoding.

In [10] proposed the SOLS technique to overcome the problem on hardware utilization of VLSI design used for the DSRC dedicated short-range communication. The DSRC standards typically adopt FM0 and Manchester codes to succeed in dc-balance, enhancing the signal irresponsibleness. Still, the coding-diversity between the FM0 and Manchester codes seriously limits the potential to style a completely reused VLSI design for each. The SOLS technique improves the hardware utilization rate from fifty seven.14% to 100% for each FM0 and Manchester encodings. In [11] proposed a method for power reduction in VLSI architecture using FM0 and Manchester encoding. Power is reduced by reducing the number of components used and improves the performance of the FM0 and Manchester encoding. These results are observed by using spice. The power consumed is 0.72 mw for Manchester encoding. The power consumption is 0.14 mw for FM0 encoding. The FM0 and Manchester encoding is widely used in dedicated short range communication. Signal reliability could be achieved in dedicated short range communications by adopting FM0 and Manchester encoding.

In [12] author present the shows the encoding technique of FMO and Manchester with SOLS technique eliminates the limitation of hardware utilization by two core techniques (a) Area Compact of Retiming (b)Sharing of Logic Operation. Using compact of area retiming, the number of transistor is reduce to 22 transistors. The sharing of logic operation combines FMO and Manchester encodings. The maximum operating frequency of Manchester, FMO encodings are 2 GHz, 900MHz and consumption of power is 1.58mW, 1.14mW respectively..

In [13] the paper presents coding diversity between FM0 and Manchester encodings that causes the limitation on hardware utilization of VLSI architecture design. The fully reused VLSI architecture using SOLS technique for both FM0 and Manchester encodings are proposed. Which can eliminates the limitation on hardware utilization. The ACR technique relocates the hardware resource to reduce the transistor count.

BLOS efficiently combines the FM0 and Manchester encodings with the identical logic components. The SOLS technique improves the Hardware Utilization Rate (HUR) from 57.14% to 100% for both FM0 and Manchester encodings. The balanced hardware architecture is realized in different CMOS technology this paper not alone develops a fully reused VLSI architecture and also exhibits an efficient performance compared with the existing works.

In [14] the limitation on hardware utilization of VLSI architecture design can be caused due to coding-diversity between FM0 and Manchester encodings. A limitation on hardware utilization of FM0 and Manchester encodings is discussed in detail. In this paper, SOLS technique is used fully reused VLSI architecture for both FM0 and Manchester encodings. The limitation on hardware utilization can be eliminating by using SOLS technique by two core techniques: area-compact retiming and balance logic-operation sharing. The area-compact retiming relocates the hardware resource to reduce the number of transistors. The balance logic operation sharing efficiently combines FM0 and Manchester encodings with the identical logic components.

In [15] proposed SOLS technique to prevent wide code diversity that limits the hardware utilization rate of such a reusable encoder. To implement a system that has its own advantages like smooth traffic control, vehicular safety etc DSRC communication protocol is used this system encode the message and transmit it to other DSRC. The data is encoded using FM0 and Manchester encoding that causes the problem and it can be overcome by using SOLS technique. The SOLS encoder is of better advantage than the normal reusable encoder in terms of device utilization. Besides the logic delay and memory usage of the system also get reduced.

In [16] presents Miller encoding which is integrated with FMO and Manchester encoding architecture for the application of Dedicated Short Range Communication (DSRC). These encodings have same similarities and clock rate embedded within the transmitted data. Using the similarities in the FMO, Manchester and Miller techniques, hardware

#### (An ISO 3297: 2007 Certified Organization)

#### Vol. 4, Issue 8, August 2016

architecture is developed by using SOLS technique. This paper develops a fully reused VLSI architecture and also exhibits a competitive performance compared with the existing works.

In [17] SOLS technique is introduced to solve the hardware utilization problem caused at the time when both the FM0 and Manchester encoding is used to encode the message in DSRC by considering two parameters area compact retiming and balance logic-operation sharing. This reduces the hardware setup problem by reducing transistor and combines FM0 and Manchester encodings with the identical logic components respectively.

In [18] in this paper, the fully reused VLSI architecture using SOLS technique for both FM0 and Manchester encodings is proposed. The SOLS technique eliminates the limitation on hardware utilization by two core techniques: area compact retiming and balance logic-operation sharing. The area-compact retiming relocates the hardware resource to reduce the transistors. The balance logic-operation sharing efficiently combines FM0 and Manchester encodings with the identical logic components. This paper is realized in 180nm technology with outstanding device efficiency. The power consumption is 29392.843nW for Manchester encoding and FM0 encoding.

#### **III. CONCLUSION**

The presented work exploits the design strategies of number of scholars and presents a brief of it. This review paper presents the common work that explain the entire circuits of FM0 encoder, Miller, Manchester and a FSM (finite state machine) for all three encoders which are designed by using VHDL (Verilog Hardware Description Languages). The concept of encoding will be used in various applications as future work.

#### REFERENCES

- Yu-Hsuan Lee, and Cheng-Wei Pan, "Fully Reused VLSI Architecture of FM0 and Manchester Encoding using SOLS Technique for DSRC Applications", IEEE Transaction on Very Large Scale Integration system Vol.23, NO.1, pp.19-29 January2015.

- IEEE Transaction on Very Large Scale Integration system Vol.23, NO.1, pp.19-29 January2015.

S.P.Ramekar, and Dr.P.N.Chatur, "A Review on Fully Utilized Architecture for FM0, Manchester and Miller Encoding Using SOLS Technique", International Journal of Innovative Research in Computer and Communication Engineering, Vol. 4, Issue 2, pp.2517-2523 February 2016.

- 3. Lalitha V, and Kathiravan S, "A Review of Manchester, Miller, and FM0 Encoding Techniques", Smart Computing Review, vol. 4, no. 6, pp.481-490 December 2014.

- 4. Bhavik Mehta, and Prof. Munmun ghosal, "Review on FM0Manchester encoder-decoder used in DSRC based Applications", International Journal on Recent and Innovation Trends in Computing and Communication, Vol. 4 Issue. 4, pp.532-535, April 2016.

- Supriya S. Garade, and P. R. Badadapure, "Review of Fully Reused VLSI Architecture of Channel Encoding Using SOLS Technique for DSRC Applications", International Journal of Science and Research (IJSR), Volume 5 Issue 4, pp.2313-2315April 2016.

M. Abinava, and T. Suganya Thevi, "Evaluation of Various Forms of DSRC System- A Review", International Journal of Engineering Science Research

- Technology, November, 2014.

T Sravan Kumar, and A. Madhukar Babu, "FM0/Manchester Encoding for DSRC Applications Using SOLS Technique", Journal Research in Electrical

- Electronics and communication, Vol.3, Issue 6.

8. Ms. Jomcy Rani Xavier, and Dr. U. A.Kshirsagar, "Fully Reconfigured VLSI architecture of FM0, Manchester and Miller", International Journal of Engineering Research and General Science Volume 4, Issue 2 pp 830-846 March. April 2016.

- Engineering Research and General Science Volume 4, Issue 2,pp.839-846 March- April, 2016.

T.Rajini, and G.Sataya Prabha, "Fully Rrused VLSI Architecture Of FM0/Manchester Encoding Using SOLS Technique For DSRC Application", International Journal of Research In Advance Engineering Technologies, Volume 5, Issue 1, pp.33-40, SEP 2015.

- International Journal of Research In Advance Engineering Technologies, Volume 5, Issue 1, pp.33-40, SEP 2015.

S.Shaik Hussain, H.Somashekar, and D.V.Srihari Babu, "R10-Design and Realization of FMO/Manchester Encoding for DSRC Application Using SOLS Technique", International Journal of Advanced Research in Education Technology, Vol. 2, Issue 3, pp.81-84 (July Sept. 2015).

- 11. S.M.Subramanian, N.Nagaraj, R.Ajin, and J.Rasathi, "R11-Power Reduction in the VLSI Architecture of FM0 and Manchester Encoding" International Journal for Scientific Research & Development Vol. 2, Issue 12, pp.861-864 2015.

- 12. V. Hemalatha, and P. Srividhya, "R12-Fully Reused VLSI Architecture of Miller Encoding using SOLS Technique for DSRC", International Journal of Advance Engineering and Global Technology, Vol.4, issue 1, pp.1718-1724, January 2016.

- Mohan R, Karthikkeyan A R, "Fully Reused VLSI Architecture for DSRC Applications Using SOLS Technique", International journal of engineering studies and technical approach, Vol.02, No. 4, pp. 137-149 April 2016.

G.Keerthana, and Mrs.M.Bhuvaneswari, "R14-Design of an Efficient Encoder for DSRC Application Using SOLS Technique" International Journal of

- 14. G.Keerthana, and Mrs.M.Bhuvaneswari, "R14-Design of an Efficient Encoder for DSRC Application Using SOLS Technique" International Journal of Advanced Research In Management, architecture, Technology & Engineering, 2016.

- Arya Krishnan, and Anusree L. S., "R15-Reusable SOLS Encoder for DSRC Applications", International Journal of Science and Research (IJSR), Volume 4 Issue 2, pp. 1874-1878 February 2015.

- A.Syed Musthaba, and J.Sathya, "Fm0ManchesterMiller Encoding for Intelligent DSRC Transportation System", IOSR Journal of Electronics and Communication Engineering, PP.172-175, February 2015.

- K.Srinath, and V.Prasad, "Design and Implementation of DSRC Encoders for Efficient Hardware Utilization" International Journal of Innovative Research in Science, Engineering and Technology, Vol. 4, Issue 7, pp.5132-5142, July 2015.

McS. BPatesh, K.Umedavi, and Dr.V.Nacarsian, "Area Efficient Encoding Technique for Pachaing Power In DSPC" International Journal of Innovative

- 18. Mr.S.PRakash, K.Umadevi, and Dr.V.Nagarajan, "Area Efficient Encoding Technique for Reducing Power In DSRC" International Journal of Innovative Research in Information Security, Volume 1, Issue 3, pp.7-12 September 2014.

### BIOGRAPHY

**Neeraj Soni** is a Post Graduate Scholar in Radharaman Institute of Technology and Science, (RITS) Rajiv Gandhi Technical University, Bhopal, India. He received Bachelor of Engineering from RGTU (RGPV) Bhopal in 2012. His research interest is design of High Speed Communication Processor.