e-ISSN: 2320-9801 | p-ISSN: 2320-9798

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN COMPUTER & COMMUNICATION ENGINEERING

Volume 10, Issue 4, April 2022

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

### Impact Factor: 8.165

9940 572 462

🙆 6381 907 438

🛛 🖂 ijircce@gmail.com

🙋 www.ijircce.com

International Journal of Innovative Research in Computer and Communication Engineering

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| <u>www.ijircce.com</u> | |Impact Factor: 8.165 |

|| Volume 10, Issue 4, April 2022 ||

| DOI: 10.15680/IJIRCCE.2022.1004159|

### ATM Database System Using VLSI Technology

Ashlesha Hatagle, Anupriya Kamble, Ajay Biradar, Nibban Ovhal, Prof. Supriya Agre

Dept. of Computer, JSCOE, Pune, India Dept. of Computer, JSCOE, Pune, India

**ABSTRACT:** The high growth of the semiconductor industry over the past two decades has put Very Large Scale Integration in demand all over the world. The basics of digital logic theory and techniques are easily understood by the design based on VLSI technology. These are the core fundamentals of the fast, high-speed complex digital circuits. The electronic industry has achieved a phenomenon growth over the last few decades, mainly due to the rapid advance in semiconductor technologies and increases the demand in VLSI.

In the growing technological world, people want their work to be very simple in order to save their time. As we know some new technology is becoming popular in banking sector, which is referred as ATMs. It makes the work of people as well as the banking sectors to be easy. ATMs help in providing money to the people nearer to the living area by saving their time so that it becoming very popular.

In this work the development of a Moore machine state diagram of an ATM controller. The developed design will be modeled using Verilog HDL language which is a Hardware Description Language (HDL) used to describe a digital system. The verification of developed model will be made by identifying the suitable test cases in a test bench. The simulation will be carried out using Modelsim tool and the intended functionality can be verified with the help of its simulation results and also it can be synthesized using the Xilinx tool.

#### I. INTRODUCTION

This project is to make an automated teller machine bank account with user account and password with that user able to withdraw deposit and view there account balance. This ATM database system allows users to perform various ATM transaction online and even change their password in case of any emergencies. Automated Teller Machine enables the clients of a bank to have access to their account without going to the bank. This is achieved only by development the application using online concepts.

When the product is implemented, the user who uses this product will be able to see all the information and services provided by the ATM, when he enters the necessary option and arguments. The product also provides services like request for cheques, deposit cash and other advanced requirement of the user. The data is stored in the database and is retrieved whenever necessary. The implementation needs ATM machine hardware to operate or similar simulated conditions can also be used to successfully use the developed product. To develop this ATM system the entire operation has been divided into the following step:

- 1. verification process

- 2. language, service and account selection

- 3. Banking services

- 4. Transactions

- 5. Special services

The program is designed in such a way that the user has to card and pin number. Once verified, he is provided a menu and he/she had to enter the option provided in the menu. For example, when the user wants to view the list of payment history than he/she had to enter the option for payment history provided in the main menu. When the option is entered alone with the respective argument,

#### International Journal of Innovative Research in Computer and Communication Engineering

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| www.ijircce.com | |Impact Factor: 8.165 |

|| Volume 10, Issue 4, April 2022 ||

#### DOI: 10.15680/IJIRCCE.2022.1004159

• The user also must be given option to browse through the pages like previous page, next page, etc. The user may experience a delay in retrieving or viewing the data, when there are many users logged on to the same bank branch system.

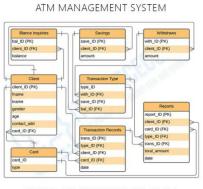

Sample ER Diagram for ATM Management System Project

ENTITY RELATIONSHIP DIAGRAM

ATM Management System ER Diagram

#### **II. LITERATURE SURVEY**

ATMs are becoming increasingly popular because they make banking functions available to all the customers around the clock, and at variety of locations, in addition to banks. In olden days ATMs are manufactured mainly by using microprocessor or microcontroller. Due to heavier demands and the falling price of computer like architectures, ATMs have moved away from custom architectures using microcontroller and / or integrated circuits to adopting hardware architecture that is very similar to a personal computer. Although it is a cheaper to use commercial hardware, it does not mean that ATMs are free from some sort of problems exhibited by the personal computers.

With the migration to commodity pc hardware, standard commercial operating systems and programming environments can be used in ATMs. Typical platforms used in ATMs include Microsoft operating systems, Sun Microsystems, Solaris, Java, Linux and UNIX may also be used in these environments. In the current scenario Linux is also playing a leading role in the ATM market place. Most of the companies are trying to use Linux operating in there ATMs

| Field                                                                          | Description                                                                            | Type                      | Length               |

|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------|----------------------|

| client_ID (PK)                                                                 | CLient ID                                                                              | Int                       | 11                   |

| fname                                                                          | Client First Name                                                                      | Varchar                   | 255                  |

| Iname                                                                          | Client Last Name                                                                       | test .                    | 11                   |

| gender                                                                         | Client Gender                                                                          | Text                      |                      |

| age                                                                            | Client Age                                                                             | Int                       | 11                   |

| contact_add                                                                    | Contact Address                                                                        | int                       | 11                   |

| Fable Nam                                                                      | e: Card                                                                                |                           |                      |

| Field                                                                          | Description                                                                            | Туре                      | Length               |

| card_ID (PK)                                                                   | Card ID                                                                                | Int                       | 11                   |

| card_number                                                                    | Card Number                                                                            | Int.                      | 11                   |

|                                                                                |                                                                                        |                           |                      |

| Fable Nam                                                                      | e: Balance Inquir                                                                      | ies                       |                      |

|                                                                                | e: Balance Inquir                                                                      | ies<br><sub>Type</sub>    | Length               |

| Field<br>Field<br>bal_ID (PK)                                                  |                                                                                        |                           | Length               |

| Field<br>bal_ID (PK)                                                           | Description                                                                            | Туре                      |                      |

| Field<br>bal_ID (PK)<br>client_ID (FK)                                         | Description<br>Balance ID                                                              | Type                      | 11                   |

| Field<br>bal_ID (PK)<br>client_ID (FK)<br>card_JD (FK)                         | Description<br>Balance ID<br>Client ID                                                 | Type<br>Int<br>Int        | 11                   |

| Field<br>bal_ID (PK)<br>client_ID (FK)<br>card_ID (FK)<br>balance              | Description<br>Balance ID<br>Client ID<br>Card ID                                      | Type<br>Int<br>Int<br>Int | 11<br>11<br>11       |

| Field<br>bal_ID (PK)<br>client_ID (FK)<br>card_ID (FK)<br>balance              | Description<br>Balance ID<br>Client ID<br>Card ID<br>Remaining Balance                 | Type<br>Int<br>Int<br>Int | 11<br>11             |

| Field<br>bal_ID (PK)<br>client_ID (FK)<br>card_ID (FK)<br>balance<br>Fable Nam | Description<br>Batance ID<br>Client ID<br>Card ID<br>Remaining Batance<br>e: Withdraws | Type<br>Int<br>Int<br>Int | 11<br>11<br>11<br>11 |

#### International Journal of Innovative Research in Computer and Communication Engineering

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| www.ijircce.com | |Impact Factor: 8.165 |

|| Volume 10, Issue 4, April 2022 ||

#### DOI: 10.15680/LJIRCCE.2022.1004159

#### III. PROPOSED METHODOLOGY AND DISCUSSION

Millions of times per day around the globe people are instantly withdrawing money at automatic teller machines (ATMs). Given the fast-pace of the world today, it is not surprising that the demand for access to quick cash is so immense. The power of ATMs would not be possible without secure connections. The final act of ATM dispending cash is the result of an amazingly fast burst of the customer never sees, but a trust is being done in a confidential manner.

#### System Analysis:

Understand the problem before the system to create analysis model there is a tendency to rush to a solution, even before the problem is understood. Develop prototypes that enables user to understand how human/machine interaction will occur. Since the perception of the quality of software is often based on the perception of the "friendliness" of the interface prototyping is highly recommended. Record the origin of and the reason for every requirement. This is the first step-in establishing traceability back to the customer . Use multiple views of requirements building data, functional and behavioral models provide the software engineer with three different views. This reduces the likelihood that something will be missed and increases the likelihood that inconsistency will be recognized.

#### IV. EXPERIMENTAL RESULTS WITH TABLES/GRAPHS/FIGURES

Use case Diagram: A use case diagram is a diagram which consists of set of usecases and actors enclosed by system boundary, and association between usecases and actors. Usecases diagram especially important in organizing, modeling the behavior of the system. Use case is a set of scenarious tied together by a common user goal. A scenario is a sequence of steps describing the interaction between a user and system. Sequence Diagram: A sequence diagram is an easy way of describing the behavior of the system. A sequence diagram shows an interaction arranged in time sequence. It has two dimensions, the horizontal dimension represents the life of the object.

#### V. CONCLUSION

Basically, ATM controller allows the user to interact with the memory and hence the security level is increased. This also makes the transaction in account gets easier. This work helps to understand the concept of Finite State Machine and designing architecture of a system. The familiarization of the procedure to develop the State Machine diagram of a system through system level analysis is improved. The ATM block diagram is studied and the corresponding Moore Machine State diagram is also analyzed. The FSM is modeled in Verilog HDL and verified for all the appropriate scenarios.

The simulation results have been verified for the different appropriate test cases. Finally the developed model is taken to the Xilinx tool and done the Synthesis using the FPGA family of Spartan 3E. Hence the maximum operating frequency of this synthesized design is given as 86.987 MHz and the minimum time period as 11.496 ns.

#### REFERENCES

- 1. Fundamentals of Software Engineering By RajibMall, Software Engineering By Ian Somerville, Analysis and Design of Information System By James Senn

- Jeongwoo Park, Kwangjae Lee, Jeonghun Kim, Kwang-Hyun Baek and Suki Kim, "An MDDI-Host Architecture with Low Complexity for SoC Platforms", IEEE Transactions on Consumer Electronics, Vol. 53, pp. 1668-1673, No. 4, Nov 2007.

- 3. S. Osborne, A.T. Erdogan, T. Arslan and D. Robinson, "Bus encoding architecture for low-power implementation of an AMBA-based SoC platform", IEE Proc. Comput. Digit. Tech., Vol. 149, pp. 152-156, No. 4, July 2002.

- 4. Cheng-Ta Hsieh and MassoudPedram, "Architectural Energy Optimization by Bus Splitting", IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 21, pp. 408-414, No. 4, Apr 2002.

- 5. Kenneth L. Calvert and Simon S. Lam, "Formal Methods for Protocol Conversion", IEEE Journal on Selected Areas in Communications, Vol. 10, pp. 127-142, No. I, Jan 1990.

- 6. Chih-Wea Wang, Chi-Shao Lai, Chi-Feng Wu, Shih-Arn Hwang, and Ying-Hsi Lin, "On-chip Interconnection Design and SoC Integration with OCP", Proceedings of the IEEE International Symposium on VLSI Design, Automation and Test (VLSI-DAT '08), pp. 25-28, 23-25 Apr 2008.

- 7. OCP-IP, "Open core protocol Specification v2.2", Document Revision 1.1, http://www.ocpip.org/, 2007.

- S. Watanabe, K. Seto, Y. Ishikawa, S. Komatsu and M. Fujita, "Protocol Transducer Synthesis using Divide and Conquer approach", Proceedings of the Asia and South Pacific - Design Automation Conference (ASP-DAC '07), pp. 280-285, 23-26 Jan 2007

## **INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH**

IN COMPUTER & COMMUNICATION ENGINEERING

🚺 9940 572 462 应 6381 907 438 🖂 ijircce@gmail.com

www.ijircce.com