e-ISSN: 2320-9801 | p-ISSN: 2320-9798

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN COMPUTER & COMMUNICATION ENGINEERING

Volume 11, Issue 12, December 2023

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

0

### Impact Factor: 8.379

9940 572 462

6381 907 438

🛛 🖂 ijircce@gmail.com

🙋 www.ijircce.com

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| www.ijircce.com | |Impact Factor: 8.379 | Monthly Peer Reviewed & Referred Journal |

Volume 11, Issue 12, December 2023

| DOI: 10.15680/IJIRCCE.2023.1112017 |

## Study of Linear Convolution using Kogge Stone Adder and Array Multiplier

Kamlesh Kumar<sup>1</sup>, Prof. Suresh. S. Gawande<sup>2</sup>

M. Tech. Scholar, Department of Electronics and Communication, Bhabha Engineering Research Institute,

Bhopal, India<sup>1</sup>

Guide, Department of Electronics and Communication, Bhabha Engineering Research Institute, Bhopal, India<sup>2</sup>

**ABSTRACT:** - On this Technical era the excessive velocity and low area of VLSI chip are very- very crucial elements. Each day quantity of transistors and different active and passive elements are drastically developing on a VLSI chip. All of the processors of the gadgets adders and multipliers are playing an essential position. An adder is a pleasing element for the designing of fast multiplier. Ultimately here want a fast adder for excessive bit edition. In this paper, they carried out of linear convolution are based on kogge stone adder and array multiplier. Offering kogge stone adder (KSA) adder presents much less additives, less path delay and better pace compare to different present KSA adder and different adders. Right here, we're evaluating the linear convolution of different-extraordinary word length from different adders.

KEYWORDS: - Ripple Carry Adder Linear Convolution, Array Multiplier, Kogge Stone Adder

#### I. INTRODUCTION

Signal processing is the technology that includes entertainment, communication, space exploration, medicine, and archaeology, etc. Sophisticated signal processing algorithms and hardware are found suitable to a wide variety of systems, from highly specialized military systems through industrial applications to low priced, high volume consumer electronics. Although, we routinely take for granted the performance of home entertainment systems such as television and multimedia entertainment and information systems, these systems are always relied heavily on state of the art signal processing. Overall as we turn to the long run, it's clear that the role of signal processing within our society is accelerating, driven simply by the convergence of communications, computers and signal processing in both the buyer arena and in advanced industrial and government applications. Signal processing can be categorized as Analog signal processing (ASP) and Digital signal processing (DSP). The DSP is the technology that is omnipresent in virtually every engineering discipline. Higher throughput arithmetic operations are essential to attain the specified performance in lots of real-time signal and image processing applications. The core computing process is obviously a multiplication routine in DSP; therefore, it's necessary for a multiplier to be fast and power efficient and so, development of a quick and low power multiplier has been a subject of interest over decades and also in the present Thesis. The convolution operation is the essential operation of digital signal and image processing. The effectiveness of circular convolution is high compared to the linear convolution as a result of successive inputs of data. Circular convolutions are the essential building blocks in the computation of FIR filters, real-time Discrete Fourier Transforms (DFT) and Fast Fourier Transforms (FFT) [1]. Linear convolution of two N point sequences can be conveniently computed by employing circular convolution i.e. utilizing the properties of DFT [2-4] or Number Theoretic Transform (NTT) [5-7]. Many of these methods require the utilization of 2N-1 point circular convolution to compute N point linear convolution of discrete time sequences.

To boost the speed of this operation, alternative methods such as the right-angle circular convolution (RCC) has now been proposed [8, 9], and a connection between this method and linear convolution is established. To compute RCC, the modified Fermat number transform (FNT) was used, whereby some adjustments needed to be designed to split the N numbers from the computation of RCC into 2N-1 numbers required by linear convolution calculation methods. In present work, a convolution circuit has also been designed using Vedic sutra.

e-ISSN: 2320-9801, p-ISSN: 2320-9798| www.ijircce.com | |Impact Factor: 8.379 | Monthly Peer Reviewed & Referred Journal |

Volume 11, Issue 12, December 2023

| DOI: 10.15680/IJIRCCE.2023.1112017 |

#### **II. LITERATURE REVIEW**

**Rahul Kamdi et al. [1],** one of the fundamental processes in digital signal processing is convolution. The mathematical process of mixing two signals to create a third signal is called convolution. Utilizing a Vedic multiplier, Urdhava Triyagbhyam Sutra or UT sutra, based on one of the sixteen Vedic mathematics sutras, linear and circular convolution processing is accelerated. The Urdhava Triyagbhyam multiplier compared to other traditional multipliers offers faster results. Multiplier having pipelining architecture is also used to compute the convolution (circular and linear) of two sequences because it speeds up the multiplication process. Xilinx ISE Design suite 14.7 software is used to carry out the simulation and synthesis using VHDL. The area and delay for 4 bit and 8 bit circular and linear convolution is computed.

**Rahul P. Kamdi et al. [2],** analog design like ADCs, DACs, and PLLs are the crucial analog circuits. Achieving the low supply voltage in data converters design is the challenge task. At the same time achieving the desired conversion rate, resolution, sampling frequency and power dissipation are becoming crucial.Now a day the demand of designing low voltage, high speed, low power consumption, less area and low-cost ADCs is increasing. To fulfill these requirements in designing of ADCs are crucial for many innovative design applications. In this work, folding and interpolation ADC architecture using trans-resistance amplifier followed by current steering folding amplifier is designed and implemented in UMC CMOS 180nm technology. This ADC provides moderated resolution.In several applications Moderated resolution ADCs with low voltage, high speed and low power are in use. Also, the demand of low voltage ADCs is increasing in the field of embedded application. This motivates us to design the folding and interpolating ADC architecture. Furthermore, synchronizing the coarse and fine converters bits is challenging task in folding and interpolation ADCs. Hence, the main aim of my work is to design low voltage folding and interpolation ADC which operates at the input frequency of85 MHz using the less silicon chip area.

**Yongxiang Cao et al. [3],** with the vigorous development of computing power, Convolutional Neural Network (CNN) is developing rapidly, and new CNN structures with more layers and better performance continue to appear. Field Programmable Gate Array (FPGA) has gradually become the best choice for people to deploy and accelerate CNNs as a current research hotspot. This paper has studied the hardware acceleration method of FPGA to implement and simulate the Softmax layer of Alexnet on Vivado 2018.1. Combined with the features of FPGA, the Cordic algorithm is used to implement basic operations such as division and exponential functions, instead of consuming floating-point arithmetic resources. The paper proposes a method to shrink the convergence domain and analyzes the errors generated by the different digits of data after quantization and fixed-point inputs. The relative error of the Softmax layer exponential function is controlled below 0.0146% by reducing the bit width which satisfied the design requirements and saved resources. This method can complete the calculation and classification of the Softmax layer in 66.5 cycles without processing the layer data at fixed points, which greatly improves the calculation speed of the Softmax layer.

**Shubhi Shrivastava et al. [4],** of late all the organization of world are approaching the high speed processor towards the fast digital communication. In this paper we are going to propose a method to develop fast convolution technique. Convolution is the bottleneck technique for digital signal processing, image processing and other signal analysis. Proposing convolution method is comprised with multiplier and adder. With this concern we need to design a fast multiplier and adder which are also main components of processor design. Calculation of partial product will be handled by Vedic Mathematics named as UrdhvaTriyagbhayam sutra. In this paper we are using Kogge Stone device for fast speed multiplication and addition. Simulation and synthesize will be done on 14.2i Spartan 3 series of Xilinx.

**Vinay et al. [5],** Adders and Multipliers play a vital role in the functioning of various systems used in communication and signal processing. Baugh Wooley and Braun multipliers employ parallel architecture and hence they are the most frequently used multipliers for signed and unsigned operations. In any system design, the three main constraints which determine the performance of the system are speed, area and power requirement. This work involves design and implementation of modified Baugh-Wooley and Braun multipliers for signed and unsigned number multiplication respectively and analysis with respect to speed and power consumption of the designed multipliers. The adder is designed using three different logics, namely, Basic CMOS, Domino and Split Path Data Driven Dynamic Logic (SPD3L). The designed adder is then used to construct the multipliers. An improvement in power and reduction in delay is observed for both the designed multipliers.

AlaaEddin Loulou et al. [6], multi-rate fast convolution (FC) has recently been introduced as an effective tool for communication waveform processing, especially for advanced multicarrier systems targeting at well-contained spectrum. These include filter bank based multicarrier waveforms and filtered OFDM schemes which are receiving

e-ISSN: 2320-9801, p-ISSN: 2320-9798 www.ijircce.com | Impact Factor: 8.379 | Monthly Peer Reviewed & Referred Journal |

Volume 11, Issue 12, December 2023

| DOI: 10.15680/IJIRCCE.2023.1112017 |

increasing attention in the 5G radio access development. Recalling that the key idea of FC is effective implementation of high-order linear filtering through frequency-domain processing, this paper investigates possibilities to reduce the complexity of FC based waveforms. Special focus is on scenarios where a relatively small part of the bandwidth is in active use, which could be the case, e.g., in low-rate machine-type communication devices. A new variant of fast-convolution filter bank (FC-FB) is developed which uses circular convolution decomposition. The narrowband variant of decomposed structure, called D-FC-FB, achieves significantly reduced complexity, which is proportional to the active bandwidth, while maintaining filtering performance equivalent to FC-FB. Therefore, this variant is considered as a low-complexity solution for low-rate devices. D-FC-FB can be used in any multicarrier scheme that utilizes filtering at subcarrier or resource block level. This paper develops closed-form complexity expressions for the case of filter bank multi-carrier with offset-QAM subcarrier modulation (FBMC/OQAM) demonstrating significant complexity reduction in a case study.

**B.** Shweta et al. [7], in digital signal Processing, the convolution and deconvolution with a totally long collection is ubiquitous in lots of application areas. The basic blocks in convolution and deconvolution implementation are multiplier and divider. They devour an awful lot of time. This paper offers a right away method of computing the discrete linear convolution, circular convolution and deconvolution. The approach is simple to study due to the similarities to computing the multiplication of two numbers. The maximum enormous factor of the proposed technique is the development of a multiplier and divider architecture based on historic Indian Vedic arithmetic sutras Urdhvatriyagbhyam and Nikhilam algorithm. The outcomes show that the implementation of linear convolution and circular convolution the usage of vedic mathematics is efficient in terms of region and pace as compared to their implementation the use of traditional multiplier & divider architectures. The coding is executed in VHDL. Simulation and Synthesis are carried out the use of Xilinx ISE layout suit 14.2.

**Aiman Badawi et al. [8],** convolution and Deconvolution has many applications in digital signal processing. Multipliers and dividers are primary blocks in convolution and deconvolution implementation. They consume much of the time. With advances in technology, many researchers have tried and are trying to layout multipliers and dividers which provide both of the following- high pace, low power consumption, regularity of layout and as a result much less region or maybe mixture of them in multiplier and divider. In this paper, the direct method is used to locate convolution and deconvolution. Discrete linear convolution of finite period sequences the usage of Urdhva Triyagbhyam set of rules is provided here. Same set of rules is likewise used for deconvolution to enhance velocity. This design method successfully and accurately hastens computation without compromising with region.

**K. Shao et al., [9],** Multiplication is an vital essential feature in mathematics operations. Multiplication-based totally operations together with Multiply and gather(MAC) and inner product are among a number of the regularly used computation extensive arithmetic functions(CIAF) presently applied in many digital sign Processing (DSP) programs such as convolution, fast Fourier rework(FFT), filtering and in microprocessors in its arithmetic and common sense unit . Considering multiplication dominates the execution time of maximum DSP algorithms, so there is a want of high velocity multiplier. Presently, multiplication time remains the dominant component in figuring out the instruction cycle time of a DSP chip.

**M. Renfors et al. [10],** digital signal Processing (DSP) operations are very important part of engineering as well as medical area. Designing of DSP operations have many strategies. For the designing of DSP operations, multiplication is play crucial function to carry out sign processing operations which includes Convolution and Correlation. The new methods of this implementation are mentally and clean to calculate of DSP operations for small duration of sequences. On this paper a fast approach for DSP operations based totally on historic Vedic mathematics is contemplated.

#### **III. DIFFERENT TYPES OF ADDER**

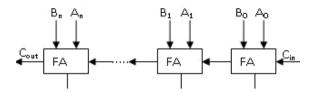

Ripple carry is a combinational circuit for adding greater than two bit records. It's also known as parallel adder. Ripple carry adder can be designed with the aid of the use of complete adder in cascading shape. Convey output of first full adder is hooked up with enter of the subsequent full adder, so bring is rippled from one adder to some other adder. This is by way of it is referred to as ripple-bring adder. Let us take example, for designing *n* bit RCA inputs are  $(A_n \dots A_2, A_2, A_1, A_0)$  and  $(B_n \dots B_3, B_2, B_1, B_0)$  then carry bits  $(C_n \dots C_3, C_2, C_1)$  and summation bits are $(C_{out} \dots S_3, S_2, S_1, S_0)$ .

e-ISSN: 2320-9801, p-ISSN: 2320-9798| www.ijircce.com | |Impact Factor: 8.379 | Monthly Peer Reviewed & Referred Journal |

Volume 11, Issue 12, December 2023

| DOI: 10.15680/IJIRCCE.2023.1112017 |

Figure 1: An n-bit Ripple Carry Adder bit binary addition

In this figure all the full adders are connected in cascading form. Bring enter is a further enter which has fixed price. First complete adder gives the convey output and summation output. Convey output of the primary complete adder is hooked up with 2nd cascading complete adder so that you can be taken into consideration as an enter bit.

#### • KOGGE STONE ADDER

Kogge Stone Adder changed into proposed by using Peter M. Kogge and Harold S. Stone. Kogge Stone Adder is a complicated generation of look a- head conveys Adder. That is also known as parallel prefix adder. It has more area than to Brent Kung Adder however less Fan-out. This adder affords the deliver sign time and turn out to be quickest adder for commercial level.

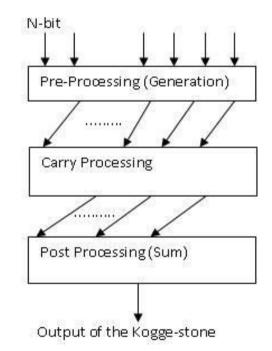

First block of KSA is Pre- Processing a good way to generate and propagate the convey. Processing of deliver may be carried out over the convey processing place and all the bring sign go through the publish processing block. Inside the pre preprocessing level we find the, generate and propagate alerts from every inputs.

$$P_n = A_n \oplus B_n \tag{1}$$

$$G_n = A_n \cdot B_n \tag{2}$$

Figure 2: A Block Structure of Kogge Stone Adder bit binary addition

Carry processing stage provides the carries corresponding to each bit. Execution of these bit operation is carried out from parallel. After finding the carries in parallel they are segmented in to smaller pieces.

$$CP_{n-1} = P_{n-1} \bigoplus P_n \tag{3}$$

$$CG_{n-1} = (P_n \bigoplus G_{n-1}) + G_n \tag{4}$$

Bottom block is summation block which provides the summation bits. That blocks are comprised with XOR gate. If one input isn't the same as any other then output will be excessive. And if inputs are identical then outputs can be low.

e-ISSN: 2320-9801, p-ISSN: 2320-9798 www.ijircce.com | Impact Factor: 8.379 | Monthly Peer Reviewed & Referred Journal |

Volume 11, Issue 12, December 2023

| DOI: 10.15680/IJIRCCE.2023.1112017 |

Kogge Stone presents the less region than to other parallel adder like deliver choose adder, convey keep adder and appearance in advance adder.

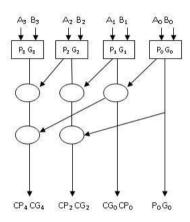

Above diagram is a functional diagram of Kogge Stone adder for 4 bit addition. Here elliptically symbol defined as a carry processing stage. The output of the preprocessing stage is fed to next carry stage and post processing as well.

Figure 3: A Functional Diagram of Kogge Stone Adder Stone Adder bit binary addition

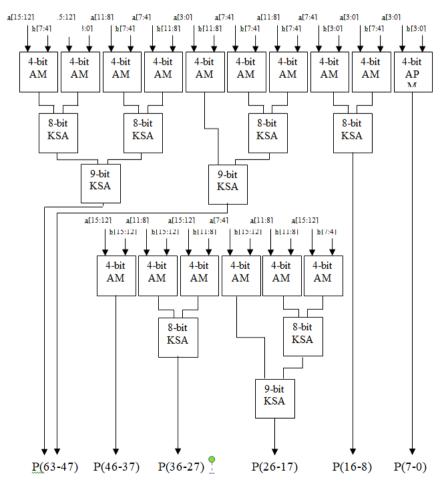

Figure 4: Linear Convolution based on array multiplier and RCA adder

e-ISSN: 2320-9801, p-ISSN: 2320-9798| www.ijircce.com | |Impact Factor: 8.379 | Monthly Peer Reviewed & Referred Journal |

Volume 11, Issue 12, December 2023

| DOI: 10.15680/IJIRCCE.2023.1112017 |

Simulation of these experiments can be done by using Xilinx 14.2I VHDL tool. In this paper we are focusing on propagation delay. Propagation delay must be less for better performance of digital circuit. Xilinx is an analysis and simulation tools which has many application in research filed. In this tool simulation is divided in to three categories, model, behavioral and structural. Xilinx 14.2i is an updated version which has many merits than other version.

#### **IV.CONCLUSION**

Multipliers are also used to calculate the Convolution which is the basic operation in LTI systems. Therefore, a new method of convolution approach has also been suggested and designed in this paper. Convolution can also be calculated easily by FFT algorithm and FFT circuit can be designed using complex multiplier. Therefore, a complex multiplier based on Vedic sutras has been designed and simulated in the present work which consumes less power and delay.

#### REFERENCES

- [1] Rahul Kamdi, Prasheel Thakre, Aniket Pathade and Sandeep Kumar Tiwari, "4 Bit and 8 Bit Convolution Using Vedic Multiplier", International Conference on Emerging Trends in Engineering and Medical Sciences (ICETEMS), IEEE 2022.

- [2] Rahul P. Kamdi, Sandip Kumar Tiwari, Aniket Pathode, "Design & implementation of fine ADC block in 8-b folding and interpolation", Second International Conference on Artificial Intelligence and Smart Energy (ICAIS), IEEE 2022.

- [3] Yongxiang Cao, Wan'ang Xiao, Jingdun Jia, Dehua Wu and Weixin Zhou, "Cordic-based Softmax Acceleration Method of Convolution Neural Network on FPGA", International Conference on Artificial Intelligence and Information Systems (ICAIIS), IEEE 2020.

- [4] <u>Shubhi Shrivastava</u> and Paresh Rawat, "High Speed and Delay Efficient Convolution by using Kogge Stone Device", International Conference on Computer Communication and Informatics (ICCCI), IEEE 2017.

- [5] I. Vinay B. Biradar, P. G. Vishwas, C. S. Chetan and B. S. Premananda, "Design and performance analysis of modified unsigned braun and signed Baugh-Wooley multiplier", International Conference on Electrical, Electronics, Communication, Computer, and Optimization Techniques (ICEECCOT), IEEE 2017.

- [6] AlaaEddin Loulou, Juha Yli-Kaakinen and Markku Renfors, "Efficient fast-convolution based implementation of 5G waveform processing using circular convolution decomposition", <u>IEEE International Conference on Communications</u> (ICC), IEEE 2017.

- [7] B. Shweta S. Tejal S. Kiran and G. Kamde Archana "Implementation of Modified Baugh Wooley Signed Multiplier" International Journal of Innovative Research in Computer and Communication Engineering (IJIRCCE) vol. 5 no. 2 pp. 2317-2321 Feb. 2017.

- [8] <u>Aiman Badawi</u>, <u>Ali Alqarni</u>, Abdullah Aljuffri and Mohammed S. BenSaleh, "FPGA realization and performance evaluation of fixed-width modified Baugh-Wooley multiplier", Third International Conference on Technological Advances in Electrical, Electronics and Computer Engineering (TAEECE), IEEE 2015.

- [9] K. Shao J. Alhava J. Yli-Kaakinen and M. Renfors "Fast-convolution implementation of filter bank multicarrier waveform processing" Proc. IEEE Int. Symp. on Circuits and Systems (IS CAS pp. 978-981 May 2015.

- [10] M. Renfors J. Yli-Kaakinen T. Levanen M. Valkama T. Ihalainen and J. Vihriala "Efficient fast-convolution implementation of filtered CP-OFDM waveform processing for 5G" Proc. IEEE Globecom Workshops (GC Wkshps) pp. 1-7 Dec 2015.

- [11] Pramod S. Aswale Mukesh P. Mahajan Manjul V. Nikumbh and Omkar S. Vaidya "Implementation of Baugh-Wooley Multiplier and Modified Baugh Wooely Multiplier using Cadence (Encounter) RTL" International Journal of Science Engineering and Technology Research (IJSETR) vol. 4 no. 2 pp. 293-298 Feb. 2015.

- [12] C.S. Chetan Vinay B. Biradar P.G. Vishwas and B.S. Premananda "Performance Enhancement of 32-bit Carry Select Adder by Employing RTL Optimization Techniques" International Research Journal of Engineering and Technology IRJET vol. 2 no. 3 pp. 2273-2277 June 2015.

- [13] Surabhi Jain and Sandeep Saini, "High Speed Convolution and Deconvolution algorithm (Based on Ancient Indian Vedic Mathematics)", 11th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology (ECTI-CON), IEEE 2014.

- [14] M. Renfors J. Yli-Kaakinen and F. J. Harris "Analysis and design of efficient and flexible fast-convolution based multirate filter banks" IEEE Transactions on Signal Processing vol. 62 no. 15 pp. 3768-3783 Aug 2014.

- [15] B.S. Premananda Samarth S. Pai B. Shashank and Shashank S. Bhat "Design of Area and Power Efficient Complex Number Multiplier" Proceedings of Fifth IEEE International Conference on Computing Communication and Networking Technologies (ICCCNT) pp. 1-5 July 2014.

- [16] Vivek V. Babu and S. Mary Vijaya Lense "Delay Optimized 16-Bit Twin Precision Baugh Wooley Multiplier" International Journal of Emerging Technology and Advanced Engineering (IJETAE) vol. 4 no. 3 pp. 90-95 March 2014.

- [17] A. Jipsa and P. Jyotirmoy "Design and Implementation of High Speed Baugh Wooley and modified Booth Multiplier using Cadence RTL" International Journal of Research in Engineering and Technology (IJRET) vol. 3 no. 8 pp. 56-63 August 2014.

## INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN COMPUTER & COMMUNICATION ENGINEERING

🚺 9940 572 462 应 6381 907 438 🖂 ijircce@gmail.com

www.ijircce.com