(An ISO 3297: 2007 Certified Organization) Website: <u>www.ijircce.com</u> Vol. 5, Issue 2, February 2017

# Implementation of Modified Baugh Wooley Signed Multiplier

Shweta Bhadange<sup>1</sup>, Tejal Salunke<sup>2</sup>, Kiran Shinde<sup>3</sup>, Asst. Prof. Kamde Archana G.<sup>4</sup>

B.E Student, Dept. of E & TC, Sir Visvesvaraya Institute of Technology, Chincholi, Nasik, Maharashtra, India

B.E Student, Dept. of E & TC,Sir Visvesvaraya Institute of Technology, Chincholi, Nasik, Maharashtra, India

B.E Student, Dept. of E & TC, Sir Visvesvaraya Institute of Technology, Chincholi, Nasik, Maharashtra, India

Assistant Professor, Dept. of E&TC., Sir Visvesvaraya Institute of Technology, Chincholi, Nasik, Maharashtra, India

**ABSTRACT**: Adders and multipliers are fundamental building blocks in many computational units. The project is implemented on Wallace signed multiplier circuit in ASIC through modified Baugh-Wooley approach using standard conventional logic gates/cells, based on complementary pass transistor logic and have been validated with simulations, a layout vs. schematic check, and a design rule check. It is proved that the proposed multiplier is better and optimized, compared to its existing counterparts with respect to the number of gates, constant inputs, garbage outputs, hardware complexity, and number of transistors required. The Baugh-Wooley multipliers exhibit comparable delay, less power dissipation and smaller area.

**KEYWORDS**: Wallace signed multiplier, Baugh-Wooley approach, and standard conventional logic cells.

## I. INTRODUCTION

Multiplication involves two basic operation generation of partial products and their accumulation. There are two possible ways to speed up the multiplication reduce the number of partial product or accelerate there accumulation. The project implemented on Wallace signed multiplier circuit in ASIC through modified Baugh-Wooley approach. Implemented by using the standard conventional logic gates/cells, based on complementary pass transistor logic and have been validated with simulations, a layout vs. schematic check, and a design rule check. Comparing to its existing counterparts with respect to the number of gates, constant inputs, garbage outputs, hardware complexity, and number of transistors required with Baugh-Wooley multipliers.

Multiplication is an important fundamental function in arithmetic logic operation. Computational performance of a DSP system is limited by its multiplication performance and since, multiplication dominates the execution time of most DSP algorithms therefore high-speed multiplier is much desired. Currently, multiplication time is still the dominant factor in determining the instruction cycle time of a DSP chip. With an ever-increasing quest for greater computing power on battery-operated mobile devices, design emphasis has shifted from optimizing conventional delay time area size to minimizing power dissipation while still maintaining the high performance. Low power consumption is also important issue in multiplier design. To reduce significant power consumption it is good to reduce the number of operation thereby reducing dynamic power which is a major part of total power consumption so the need of high speed and low power multiplier has increased. Designer mainly concentrate on high speed and low power efficient circuit design. The objective of a good multiplier is to provide a physically packed together, high speed and low power consumption unit.

## II. LITERATURE REVIEW

Charles R. Baugh and Bruce A. Wooley, member of IEEE presents "A Two's complement parallel Array Multiplication Algorithm" in 1973. In this two's complement, m-bit by n-bit parallel array multiplication is described. As multiplication is an essential function in digital system due to its necessity in operation of digital filters and Fourier transform processor. This paper presents an algorithm for parallel two's complement multiplication. The advantage of

(An ISO 3297: 2007 Certified Organization)

Website: <u>www.ijircce.com</u>

#### Vol. 5, Issue 2, February 2017

the algorithm is the sign of all the partial products bits are positive, which allow the product to be formed using array addition technique. The drawback of the proposed algorithm is the need for the complements of each multiplier and multiplicand bit. [4] AswathySudhakar et al in 2010 proposed "High Speed Power-Efficient Modified Baugh-Wooley Multipliers", in this in this they proved modified Baugh-Wooley multiplier. Here comparison of various multiplier architecture for VLSI application. The baugh-wooley multiplier found to be best suited for the multiplication functionality according to resolution and efficiency. [10] K'Andrea et al presents, "Analysis of column compression multipliers" in 2001. This paper tests the proficiency of the area, delay and power characteristic of Dadda and Wallace multiplier. As operand word length increases, column compression multiplier increases roughly. Simulation indicate that, Wallace multipliers have 4% to 7% more area than equivalent Dadda multiplier, and approximately the same delay for operand sizes from 8 to 64 bits. [11] Andrew D. Booth present "A signed binary multiplication technique". In this a technique is described by which binary numbers of either sign may be multiplied together by a uniform process which is independent. In the design of automatic computing machines it is necessary to have two numbers whose signs are not necessarily positive. [12]

#### III. METHODOLOGY

#### • Baugh Wooley Multiplier

Baugh wooley technique was developed to design direct multipliers for complement numbers [1]. When multiplying complement number directly each of the partial products to be added is a signed number. Thus each partial product has to be sign extended to the width of final product in order to form the correct by carry save adder tree. According to Baugh wooley approach, an efficient method of adding extra entries to bit matrix is suggested to avoid having to deal with negatively weighted bits in partial product matrix. Baugh Wooley method increases the height of longest column by two, which may lead to greater delay through the carry save Adder tree.

Modified form of Baugh wooley method is more preferable since it does not increase the column in the matrix. However this is type of multiplier is suitable for application where operand with less than 32 bit are processed like digital filter where small operand like 6,8,12 bits are used. Baugh wooley scheme become slowly and area consuming when operand greater than and equal to 32 bit.

## IV. **PROPOSED ALGORITHM**

To compute product of two signed numbers we have used modified Baugh-Wooley approach [4]. Conventional multiplier design is divided into two parts: partial product generation circuit and then multi-operand addition circuit.

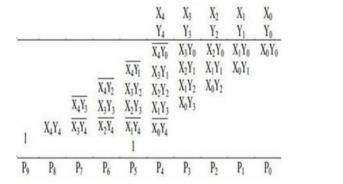

Fig.1. Modified Baugh-Wooley 5 x 5 Signed Multiplier

#### A. DESIGN OF CONVENTIONAL MULTIPLIER

First to compute partial product, 17 ANDs and 8 NANDs are used to employ the procedure given in Fig. 1. Aftergenerating partial products, next step is a multi-operandaddition. The bits of each column should be added given

(An ISO 3297: 2007 Certified Organization)

Website: <u>www.ijircce.com</u>

## Vol. 5, Issue 2, February 2017

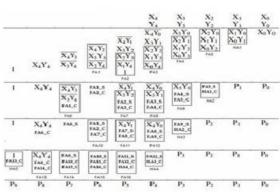

in Fig.1. To add these bits, FA and HA are used. The bits should added in such a way that our circuit will give the best results. Figure 2 shows the way of adding these bits in our proposed circuit. The Wallace approach has been used to construct acircuit with less delay. To minimize delay in our proposed circuit, P9 is computed by inverting carry output from earlier (FA13). The resulting circuit for multi-operand additionneeds one 1-NOT gate, 4-HA and 16-FA as shown in fig.2. [2].

## B. **PROPOSED ALGORITHM**

- To implement conventional multiplier using technology CMOS 600micrometer, structural Verilog code is written for the circuit.

- Then by using digital design flow from Cadence which uses :

- I. Cadence Encounter RTL Compiler.

- II. Encounter RTL-to-GDSII System.

- Then by using analog design flow from Cadence which uses :

- I. Virtuoso Schematic.

- II. Layout Editor Tools.

- Conventional multiplier is implemented with schematic and Layout.

## V. SIMULATION RESULTS

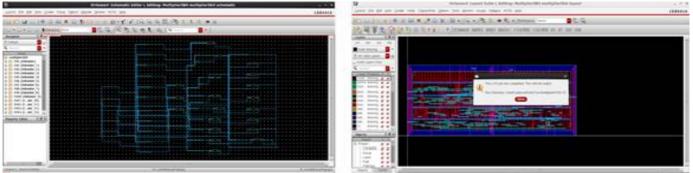

Semi-custom ASIC design is carried out using Cadence tool [3]. To implement conventional multiplier, structural Verilog code is written for the circuit shown in Fig. 2. Then by using digital design flow from Cadence which uses Cadence Encounter RTL Compiler, Encounter RTL-to-GDSII System, Virtuoso Schematic and Layout Editor tools, we implemented conventional multiplier, schematic and Layout is shown in Fig. 3 and Fig. 4.

Fig.3. Schematic for Conventional Multiplier

Fig.4. Layout and LVS match for Conventional Multiplier

For conventional multiplier, Schematic were validated by electrical simulations using Spectre, Layout has been successfully validated by the DRC and LVS check has successfully validated the functionality with respect to the schematic. For simulation of schematic and analog extracted view we written Digital Vector file which generates stimuli and performs vector check according to digital vectors using Virtuoso UltraSim Simulator, which is used in Virtuoso Spectre Mode. Finally the post extraction simulation is carried out for the circuits and calculated power dissipation values as shown in Fig. 5 and Fig. 6 for conventional multiplier.

(An ISO 3297: 2007 Certified Organization)

Website: <u>www.ijircce.com</u>

## Vol. 5, Issue 2, February 2017

file for conventional multiplier

Fig 6. Power dissipation after post extraction simulation for Conventional Multiplier

## VI. RESULTS

The table 1 shows the result of conventional multiplier where circuit is implemented by semi-custom ASIC design. It shows result in terms of power dissipation, numbers of transistors required and total area required for actual implementation of conventional multiplier circuit.

| MULTIPLIER              | PROCESS                                         | POWER       | TRANSISTOR | PLACE   | TOTAL                              |

|-------------------------|-------------------------------------------------|-------------|------------|---------|------------------------------------|

| DESIGN                  | TECHNOLOGY                                      | DISSIPATION | REQUIRED   | ROUTE   | AREA                               |

| Conventional<br>circuit | AMI06(C5N<br>0.6u)CMOS<br>Process<br>Technology | 6.486mw     | 810        | By Tool | 389umX156um,<br>With Power<br>ring |

Table 1. Results for proposed conventional signed multiplier circuit

#### VII. CONCLUSION AND FUTURE WORK

In this way, the Baugh Wooley signed Multiplier is implemented. It is proving that not only the proposed multiplier is better and optimized, compared to its existing counterparts with respect to the number of gates, constant inputs, garbage outputs, hardware complexity, and number of transistors required, but also results in low power dissipation in conventional logic design. Also, the standard cells were implemented in 0.6m CMOS using complementary pass transistor logic. These cells are prototype cells and knowledge for future improvements.

The proposed conventional multiplier placement and routing can be carried out by tool like Cadence Encounter. Optimization can be done by reducing the number of gates, or the circuit delays, but in this case it would also allow us to improve the placement and routing of cells. Number of required transistor can further be decreased in the implementation of multi-operand addition.

## REFERENCES

- [1] Neil Weste, Kamran Eshraghin, "Principles of CMOS VLSI Design", Second Edition, 2002.

- [2] Hatkar A. P., Hatkar A. A, "ASIC Design of Reversible Multiplier Circuit", International Conference on Electronic Systems, Signal Processing and Computing Technologies, IEEE, PP 47-52, 2014.

- [3] Erik Bruvand "Digital VLSI Chip Design with Cadence and Synopsys CAD Tools", Pearson, 1 Edition.

- [4] Ch. Baugh, B.A. Wooley, "A two's complement parallel array multiplication algorithm", IEEE Transactions on Computers C-22, 1973, 12.

- [5] Kang, Sung-Mo; Leblebici, Yusuf, "CMOS Digital Integrated Circuits: Analysis and Design", Tata McGraw-Hill, 2004.

- [6] Priya Saxena and Rajan Chaudhary, "Custom Digital Design of High Speed 8 Bit Multiplier Using Cadence Tool", ISSN 2231-1297, Volume 3, Number 4 (2013), pp. 491-496 © Research India Publications, 2013.

(An ISO 3297: 2007 Certified Organization)

Website: www.ijircce.com

#### Vol. 5, Issue 2, February 2017

- [7] Vinod Sajjan, B.Sajidha Thabassum, Mala Sinnoor,"Design and Implementation of 4-Bit Unsigned Array Multiplier and Baugh Wooley Multiplier using CMOS 180nm Technology and Their Comparative Analysis"ISSN 2319-8885, Vol.04,Issue.02 ,Pages:0276-0282, January-2015.

- [8] Shruti D. Kale, Prof. Gauri N. Zade, "Design of Baugh-wooley Multiplier using Verilog HDL", IOSRJournal of Engineering(IOSRJEN), ISSN(e):2250-3021, ISSN(p):2278-8719, Vol.05, Issue 10, ||V2||PP 25-29, October, 2015.

- [9] Pramodini Mohanty, "An Efficient Baugh-Wooley Architecture for Signed & Unsigned Fast Multiplication", NIET Journal of Engineering & Technology, Vol. 1, Issue 2, 2013.

- [10] AswathySudhakar, D. Gokila VLSI Design Group Department of ECE, "High-Speed Power-Efficient Modified Baugh-Wooley Multipliers", 978-1-4244-7057-0/10@2010 IEEE.

- [11] K'Andrea C. Bickerstaff, Michael J. Schulte, and Earl E. Swartzlander, Jr., "Reduced Area Multipliers," Proceedings of the 1993 International Conference on Application Specific Array Processors, pp. 478-489, 1993.

- [12] M. Mehta, V. Parmar, and Earl E. Swartzlander, Jr., "High-Speed Multiplier Design Using Multi-Input Counter and Compressor Circuits", Proceedings of the 10th Symposium on Computer Arithmetic, pp. 43-50, 1991.

- [13] IndrayaniPatle, AkanshaBhargav, Prashant Wanjari, "Implementation of Baugh-Wooley Multiplier Based on Soft-Core Processor," IOSR Journal of Engineering (IOSRJEN), pp. 01-07, October. 2013.