ISSN(O): 2320-9801 ISSN(P): 2320-9798

# International Journal of Innovative Research in Computer and Communication Engineering

(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

Impact Factor: 8.771

Volume 13, Issue 4, April 2025

⊕ www.ijircce.com 🖂 ijircce@gmail.com 🖄 +91-9940572462 🕓 +91 63819 07438

DOI:10.15680/IJIRCCE.2025.1304160

www.ijircce.com | e-ISSN: 2320-9801, p-ISSN: 2320-9798| Impact Factor: 8.771| ESTD Year: 2013|

International Journal of Innovative Research in Computer and Communication Engineering (IJIRCCE)

(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

## Performance Evaluation of 6t,7t,8t & 9t Sram Cell Topologies at 22nm Technology Node

#### J.Jyothiswaroop

Assistant Professor, Department of ECE, Sri Vasavi Institute of Engineering & Technology (Autonomous),

Nandamuru, Pedana, A.P, India

#### P.M.N.Radhakrishna, R.Nagamani, V.Venu Madhav, N.S.Vamsikrishna

Department of ECE, Sri Vasavi Institute of Engineering & Technology (Autonomous), Nandamuru, Pedana, A.P, India

**ABSTRACT**: SRAM (Static Random Access Memory) has become a major key component in many VLSI Chips, due to its high storage density and quick access time, it has become a popular data storage device. SRAM has played a significant role in the global VLSI sector. Due to the significant increase of low power and low voltage memory systems in recent times, SRAM has been prioritised in the research sector. This is owing to the increased demand for high-end devices, IC memory cards, and other communication devices, as well as the advancement of portable battery-operated devices. The power and area of a low power 6T,7T,8T&9T cell design are assessed in this research. This work describes the design and implementation of a 6T,7T,8T&9T SRAM cell in standard CMOS process technology at 22nm node. In the Tanner EDA Software, this simulation was run. An improvement has been obtained both in terms of Power, Area and Delay.

KEYWORDS: SRAM, Low Power Design, 22nm Technology, Tanner EDA, Power and Area Optimization

#### I. INTRODUCTION

The continuous scaling of CMOS technology, as predicted by Moore's Law, has driven significant advancements in Very Large Scale Integration (VLSI) design. As feature sizes shrink to the 22nm node and beyond, new challenges such as increased leakage currents, reduced device reliability, and process variations have become critical, especially in memory circuits like Static Random Access Memory (SRAM).SRAM is widely used in modern processors and System-on-Chip (SoC) architectures due to its high speed and low power consumption. However, conventional 6T SRAM cells suffer from reduced read stability, limited write margins, and higher susceptibility to noise at lower supply voltages and advanced nodes. These limitations hinder their performance in ultra-low power and high-speed applications.Advanced SRAM topologies such as 7T, 8T, and 9T have been proposed to address these issues. These designs improve robustness by modifying transistor arrangements and separating read and write paths, enhancing stability under aggressive scaling conditions. Despite occupying larger areas, these cells offer improved performance in terms of read stability, noise margins, and overall reliability. This project aims to simulate and analyze 6T, 7T, 8T, and 9T SRAM cell topologies at the 22nm technology node using Tanner EDA tools. Key performance parameters such as read and write delay, static noise margin (SNM), power consumption, and cell area will be evaluated. The comparative study provides insights into the suitability of each topology for low-power, high-performance VLSI applications, particularly in embedded systems and SoCs.

#### **II.PROPOSEDSYSTEM**

This work focuses on the design and performance analysis of 6T, 7T, 8T, and 9T SRAM cells using 22nm CMOS technology. Each topology offers different trade-offs in terms of stability, power, and performance.

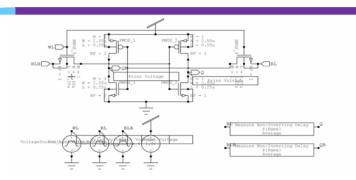

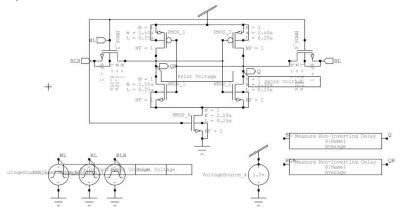

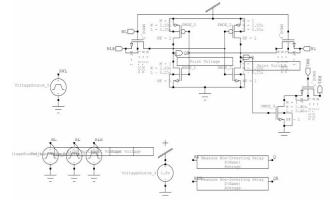

#### 6TSRAMCell:

The 6T cell consists of two cross-coupled inverters and two access transistors. During read and write operations, the word line enables the pass transistors, allowing data transfer through the bit lines. However, simultaneous switching can cause short-circuit currents, leading to static power loss and reduced stability.

www.ijircce.com

### International Journal of Innovative Research in Computer and Communication Engineering (IJIRCCE)

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| Impact Factor: 8.771| ESTD Year: 2013|

(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

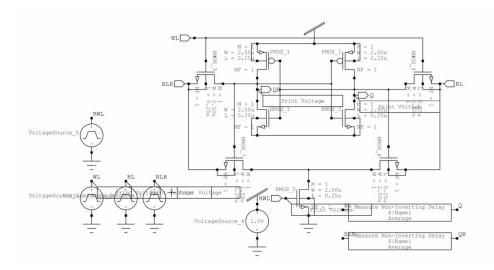

Fig.1: Schematic Diagram of 6T SRAM Cell

#### 7TSRAMCell:

An additional NMOS transistor is added to control feedback between the inverters, reducing power loss and improving read stability. During writing, feedback is cut off to ease data insertion, and during reading, the feedback path is reconnected for stable operation.

Fig.2: Schematic Diagram 7T SRAM Cell

#### 8TSRAMCell:

The 8T cell isolates the read and write operations by introducing separate access paths. This enhances read stability and prevents disturbance during reads. It uses precharged read bit lines and read word lines to sense data without altering storage nodes.

Fig.3: Schematic Diagram 8T SRAM Cell

#### 9TSRAMCell:

The 9T architecture enhances data stability by decoupling read and write paths even further. It uses differential sensing and separate word lines (RWL and WWL), which significantly improves noise margins and read reliability, especially under low-voltage and variation-prone conditions. The read operation is performed through a dedicated read path that minimizes the disturbance to internal storage nodes, ensuring better robustness against bit flipping and improved sensing accuracy. Additionally, by isolating the write path, the cell becomes more tolerant to process variations and aging effects.

These designs are simulated and compared in terms of key performance metrics such as read/write delay, static noise margin (SNM), power consumption, and cell area using Tanner EDA tools. The comparative analysis under various voltage levels and process corners aims to determine the most suitable SRAM topology for modern low-power, high-performance applications.

Fig.4: Schematic Diagram of 9T SRAM Cell

#### **III. EXPERIMENTAL RESULTS**

#### **6T SRAM Cell Results:**

| T-Spice - (6TSRAM.out)                       | - 0 1            |  |

|----------------------------------------------|------------------|--|

| 🚰 File Edit View Simulation Tab              | - 1              |  |

| ★ ▶ ■ 1                                      | 2 0 0            |  |

|                                              |                  |  |

| * BEGIN NON-GRAPHICAL DATA                   |                  |  |

| Power Results                                |                  |  |

| wdd gnd from time 0 to le-                   |                  |  |

| Average power consumed -> :                  |                  |  |

| Max power 3.832061e-005 at                   |                  |  |

| Min power 3.119881e-008 at                   | ime 3.02881e-010 |  |

|                                              |                  |  |

| * END NON-GRAPHICAL DATA                     |                  |  |

|                                              |                  |  |

| * BEGIN NON-GRAPHICAL DATA                   |                  |  |

| MEASUREMENT RESULTS                          |                  |  |

| TRAN_Measure_Delay_1 = 2.0                   | 19e-007          |  |

| TRAN_Measure_Delay_2 = 8.24                  | 15e-010          |  |

| * END NON-GRAPHICAL DATA                     |                  |  |

| *                                            |                  |  |

| * Parsing                                    | 0.01 seconds     |  |

| * Setup                                      | 0.01 seconds     |  |

| * DC operating point<br>* Transient Analysis | 0.00 seconds     |  |

| <ul> <li>Transient Analysis</li> </ul>       | 0.03 seconds     |  |

| • Overhead                                   |                  |  |

| * Total                                      | 2.45 seconds     |  |

| * Simulation completed                       |                  |  |

| * End of T-Spice output fil                  | i                |  |

|                                              |                  |  |

Fig.5: Power Consumption results of 6T SRAM Cell

www.ijircce.com

### International Journal of Innovative Research in Computer and Communication Engineering (IJIRCCE)

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| Impact Factor: 8.771| ESTD Year: 2013|

(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

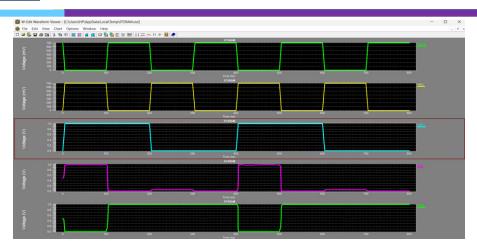

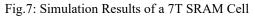

#### **7T SRAM Cell Results**

Fig.7: Power Consumption results of 6T SRAM Cell

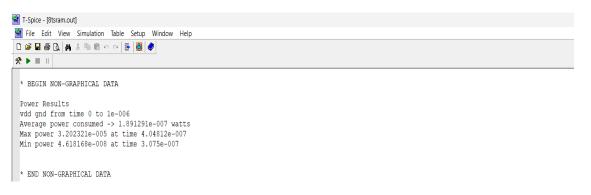

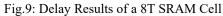

#### **8T SRAM Cell Results**

Fig.10: Simulation Results of a 8T SRAM Cell

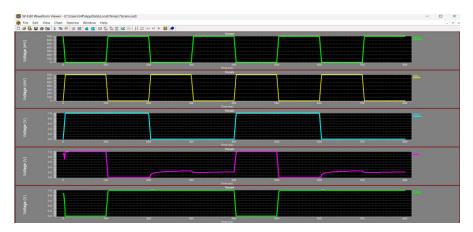

#### 9T SRAM Cell Results

| T-Spice - [Simulation Status]                       |                                |  |  |  |

|-----------------------------------------------------|--------------------------------|--|--|--|

| 📽 File Edit View Simulation Table Setup Window Help |                                |  |  |  |

|                                                     |                                |  |  |  |

|                                                     |                                |  |  |  |

|                                                     |                                |  |  |  |

| nput file: 9tsram.sp                                | Output: 9tsram.out             |  |  |  |

| ragress: Simulation completed                       | compar. His biccon             |  |  |  |

| rugress. Sinouton competed                          |                                |  |  |  |

| atal nodes: 46 Active dev                           | ces: 9 Independent sources: 5  |  |  |  |

| otal devices: 14 Passive de                         | vices: 0 Controlled sources: 0 |  |  |  |

| Transmission lines - 0                              | Coupled transmission lines - 0 |  |  |  |

| Voltage sources - 5                                 |                                |  |  |  |

| VCVS - 0                                            |                                |  |  |  |

| CCVS - 0                                            |                                |  |  |  |

| V-control switch - 0                                |                                |  |  |  |

| Macro devices - 0                                   |                                |  |  |  |

| HDL devices - 0                                     |                                |  |  |  |

| Subcircuits - 0                                     |                                |  |  |  |

| Independent nodes - 4                               |                                |  |  |  |

| Total nodes - 4                                     | 0                              |  |  |  |

| Measurement result summ                             | 5 may                          |  |  |  |

| TRAN Measure Delay 1                                |                                |  |  |  |

| TRAN Measure Delay 2                                |                                |  |  |  |

|                                                     |                                |  |  |  |

| Parsing                                             | 0.04 seconds                   |  |  |  |

| Setup                                               | 0.01 seconds                   |  |  |  |

| DC operating point                                  | 0.06 seconds                   |  |  |  |

| Transient Analysis                                  | 0.05 seconds                   |  |  |  |

| Overhead                                            | 1.63 seconds                   |  |  |  |

|                                                     |                                |  |  |  |

| Total                                               | 1.80 seconds                   |  |  |  |

| Simulation completed                                |                                |  |  |  |

| [                                                   |                                |  |  |  |

|                                                     |                                |  |  |  |

Fig.11: Power consumption results of 9T SRAM Cell

© 2025 LJIRCCE | Volume 13, Issue 4, April 2025 www.ijircce.com [e-ISSN: 2320-9801, p-ISSN: 2320-9798] Impact Factor: 8.771 | ESTD Year: 2013] International Journal of Innovative Research in Computer and Communication Engineering (JJIRCCE) (A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

Fig.12: Simulation Results of 9T SRAM Cell

#### **IV. CONCLUSION**

The conclusion of the performance evaluation and comparison of 4T, 6T, 7T, 8T, and 9T SRAM at the 22nm technology node provides valuable insights into the characteristics and suitability of each SRAM cell design. the choice of SRAM cell design should be based on a thorough understanding of the application's requirements and trade-offs. While lower-transistor-count designs like the 4T and 6T SRAM cells may offer advantages in terms of area and speed, higher-transistor-count designs like the 9T SRAM cell provide enhanced stability and reliability, albeit at the cost of increased power consumption and area. Future research may focus on further optimizing SRAM cell designs to achieve a balance between performance, power efficiency, and area occupancy in advanced technology nodes.

#### REFERENCES

- [1] J. Ashwani, K. Deepa, K. Charan Kumar, and B. Karthick presented a paper titled "Performance Analysis of Different SRAM Cells and Proposed 9T SRAM Cell" at the 2023 8th IEEE International Conference on Communication and Electronics Systems (ICCES 2023), published in IEEE Xplore with Part Number CFP23AWO-ART and ISBN 979-8-3503-9663-8.

- [2] Debasis Mukherje, Hemanta Kr. Mondal, and B. V. R. Reddy discussed "Static Noise Margin Analysis of SRAM Cell for High Speed Application" in the IJCSI International Journal of Computer Science Issues, Volume 7, Issue 5, published in September 2020, with ISSN (Online): 1694-0814.

- [3] Prashant Upadhyay, S. K. Chhotray, R. Kar, D. Mandal, and S. P. Ghoshal analyzed "Write Stability Analysis of 8-T Novel SRAM Cell for High Speed Application" in the proceedings of the 2019 3rd IEEE International Advance Computing Conference (IACC).

- [4] Hansraj, A. Chaudhary, and A. Rana presented "Ultra Low Power SRAM Cell for High Speed Applications using 90nm CMOS Technology" at the 2020 8th International Conference on Reliability, Infocom Technologies and Optimization (ICRITO), published on pages 1107–1109 with DOI: 10.1109/ICRITO48877.2020.9197869.

- [5] K. Khare, N. Kulade, and P. Deshpande contributed the paper "VLSI Design and Analysis of Low Power 6T SRAM Cell using Cadence Tool" at the IEEE International Conference on Semiconductor Electronics (ICSE-2008), published on pages 117–121 in 2008.

- [6] S. Akashe, N. Tiwari, and R. Sharma presented "Simulation and Stability Analysis of 6T and 9T SRAM Cell in 45 nm" at the 2nd International Conference on Power, Control and Embedded Systems (ICPCES-2012), published on pages 1–6 in 2012.[7] S. Chopade and D. Padole studied "Stability Analysis of 6T SRAM Cell for Nanoscale FD-SOI Technology" and presented their findings at the Annual IEEE India Conference (INDICON-2014), with the paper published on pages 1–6

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

# **INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH**

IN COMPUTER & COMMUNICATION ENGINEERING

🚺 9940 572 462 应 6381 907 438 🖂 ijircce@gmail.com

www.ijircce.com